ISBN: 978-93-85100-14-7

# **IOTIMES - 2017**

Proceedings of International Conference on Latest Trends in Electronics and Communication (ICLTEC)

Under the Auspices of International Conference on trends in Information, Management, Engineering and Sciences (ICTIMES)

Dr. Sridhar Ganapathy

Dr. M. Thamarai

Dr. P. John Paul

## **ICTIMES - 2017**

ISBN: 978-93-85100-14-7

**Proceedings of International Conference on Latest Trends in Electronics and Communication (ICLTEC)**

Sri Ch. Malla Reddy, Founder Chairman, MRGI (Member of Parliament, Govt., INDIA)

#### Patrons:

**Chief Patron:**

Mr. Ch. Mahender Reddy, Secretary MRGI Dr. Ch. Bhadra Reddy, Treasurer MRGI

#### International Advisory Committee:

Col. G. Ram Reddy, Director (Admin), MRGI Mr. N Sudhir Reddy, Director, Administration, MRCE Dr. S. R. C. Murthy, University of Sydney, Australia Dr. A.V. Vidya Sagar, BELL, USA Dr. K.V.S. S. Narayana Rao, NITIE, Bombay Dr. K. Vijay Kumar, CEO, First ESCO India, Vizag Dr. Ch. A.V. Prasad, Senior Consultant, TCS Dr. A. Govardhan, Principal, JNTUH Dr. B. Sudeer Prem Kumar, Chairman, BOS, JNTUH Dr. K. Venkateswar Rao, JNTUH Dr. K. Venkateswar Rao, JNTUH Dr. B.N. Bhandari, Director DAP, JNTUH Dr. M. Manzoor Hussain, Director Administrations, JNTUH

Dr. M. Madhavi Latha, Former Director, I-Tech, JNTUH

Dr. V.C.V. Prathap Reddy, RIT Rochester, USA

Dr. S. Venkateswara Rao, Head- Physics, JNTUH

Mr. N. Shyam Kumar, Group Manager, Tech Mahindra

Mr. S. Goutam, Manager, TCS

Dr. Hussain Reddy, SKU, A.P.

Dr. Seow Ta Wee, University Tun Hussein Onn Malaysia.

Ir. Dr. Goh Hui Hwang, Malaysia

Chief Guest: Dr. T.G Thomas, Dean-Admissions (Campus Wide) -BITS Pilani, Dubai Campus, Academic City, Dubai, UAE.

Guest of Honor: Dr. Balajied Lang Nongrum, Biola University USA.

### Keynote Speakers: Dr. T.G Thomas,BITS Pilani,Dubai UAE Dr. Balajied Lang Nongrum, Biola University USA Dr. C. Krishna Mohan, IIT Hyderabad Dr. R.Thundil Karuppa Raj, VIT University Dr. K. Ramulu, Central University, Hyderabad

Conference General Chair: Dr. P John Paul, Principal, MRCE

## MALLA REDDY COLLEGE OF ENGINEERING (MRCE)

Permanently Affiliated to JNTUH, Approved by AICTE (New Delhi), Accredited by NBA, An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad, India - 500 100. www.mrce.in

Microsoft

## **ICTIMES - 2017**

ISBN: 978-93-85100-14-7

**Microsoft**

**Proceedings of International Conference on Latest Trends in Electronics and** Communication (ICLTEC)

#### **Organizing Committee:**

Dr. M. Thamarai, Dean Academics (Chair)

Dr. V. Bhoopathy, Dean R&D - CSE

Dr. P.Velmurgan, Dean R&D - MECH

Dr. Nikhil Raj, Dean R&D - ECE

Dr. Ch. Shankar , Dean Academics - MBA

Dr. J. Gladson, Dean Student Affairs - CSE

### Co- ordination Committee: Prof. Rajesh Durgam Prof. M. Shiva kumar Prof. Ch. Vijaya Kumari Prof. C. Shashi Kanth Prof. J. Shashi Kumar

#### Program Committee

Dr. T. V. Reddy, Vice Principal (Chair) Dr. T. Sunil, Dean Academics - CSE Dr. S.S Gowda, Dean Academics - MECH Dr. G. Sridhar, Dean Student Affairs - ECE Dr. A. Karthikeyan, Dean Student Affairs - MECH Information Contact: Dr. P John Paul Principal, MRCE +91-9348161222, 9346162620 E-mail: principal@mrce.in

## MALLA REDDY COLLEGE OF ENGINEERING (MRCE)

Permanently Affiliated to JNTUH, Approved by AICTE (New Delhi), Accredited by NBA, An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad, India - 500 100. www.mrce.in

Microsoft

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

Best Wishes:

I Congratulate ECE Department on Conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

# Best Wishes:

We Congratulate ECE Department on Conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

Col. G. Ram Reddy Director/Administrations, MRGI

Sri. N. Sudhir Reddy Director, MRCE

## Best Wishes:

We Congratulate ECE Department on Conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

## Best Wishes:

Technology has to be invented or adopted. My wishes to ECE Department on Conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

Best Wishes:

My warmest congratulations to you, MRCE and all staff on conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi),Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

Dr. Balajied Lang Nongrum

Biola University, USA.

Best Wishes:

My warmest congratulations to you, MRCE and all staff on conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

Permanently Affiliated to JNTUH, Approved by AICTE(New Delhi), Accredited by NBA An ISO 9001:2015 Certified Institution. Maisammaguda, Hyderabad - 500 100. www.mrce.in

Dr. M. Thamarai HOD - ECE Dept, MRCE

Dr. G. Sridhar Prof. ECE Dept, MRCE

# Best Wishes:

We Congratulate ECE Department on Conducting International Conference on "Latest Trends in Electronics and Communication" (ICLTEC)

| S. No.   | Title                                                                             | Page<br>No. |  |  |  |  |

|----------|-----------------------------------------------------------------------------------|-------------|--|--|--|--|

| IC17EC01 | VIDEO ENHANCEMENT USING CONTRAST LIMITED ADAPTIVE<br>HISTOGRAM EQUALIZATION       | 1           |  |  |  |  |

|          | B.Prabhakar, D.Krishnareddy                                                       |             |  |  |  |  |

| IC17EC02 | OPTIMIZED MULTI-WAVELET BASED IMAGE COMPRESSION<br>MODEL FOR MEDICAL APPLICATIONS | 10          |  |  |  |  |

|          | S.Jagadeesh, Dr.E.Nagabhooshanam                                                  |             |  |  |  |  |

|          | A FRAMEWORK FOR UNDERWATER IMAGE ENHANCEMENT                                      |             |  |  |  |  |

| IC17EC03 | AND OBJECT DETECTION                                                              | 19          |  |  |  |  |

|          | Thamarai M , Dhivyaa S P                                                          |             |  |  |  |  |

|          | A LOW FREQUENCY NOISE CANCELLATION VLSI CIRCUIT                                   |             |  |  |  |  |

| IC17EC04 | DESIGN USING LMS ADAPTIVE FILTER FOR INEAR                                        | 23          |  |  |  |  |

|          | HEADPHONES.                                                                       |             |  |  |  |  |

|          | Manu M Rajan, R.Dinesh                                                            |             |  |  |  |  |

|          | PATH LOSS CALCULATION IN WBAN AT CM3 CHANNEL BY                                   |             |  |  |  |  |

| IC17EC05 | USING PRINTED DIPOLE ANTENNA                                                      | 28          |  |  |  |  |

|          | Dinesh Sharma, Purnima K Sharma                                                   |             |  |  |  |  |

|          | CONSISTENT DATA DELIVERY IN MOBILE ADHOC NETWORKS                                 |             |  |  |  |  |

| IC17EC06 | R.Nanda Kumar, Dr.Sankara Malliga G                                               |             |  |  |  |  |

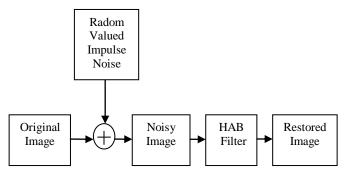

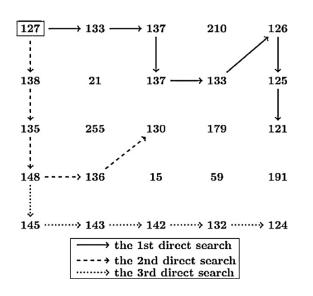

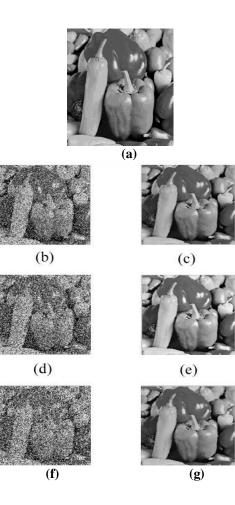

|          | DENOISING OF IMAGE CORRUPTED BY RANDOM VALUED                                     |             |  |  |  |  |

| IC17EC07 | IMPULSE NOISE USING HOMOGENEOUS AMOUNT BASED FILTER                               |             |  |  |  |  |

|          | Sathyapriya.N, Nandhini.V                                                         |             |  |  |  |  |

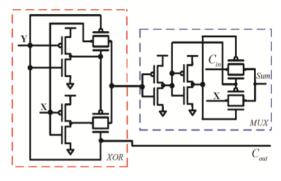

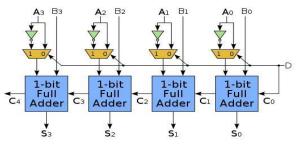

|          | NOVEL ENERGY EFFICIENT CARRY SKIP ADDER BASED                                     |             |  |  |  |  |

| IC17EC08 | ON DUAL MODE LOGIC DESIGN                                                         | 41          |  |  |  |  |

|          | Ms.C.Aishwarya, Mr R .Rajasekaran. Mrs.J.R.Beny, G.Abirami                        |             |  |  |  |  |

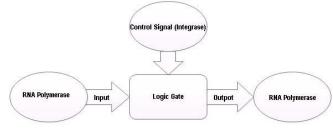

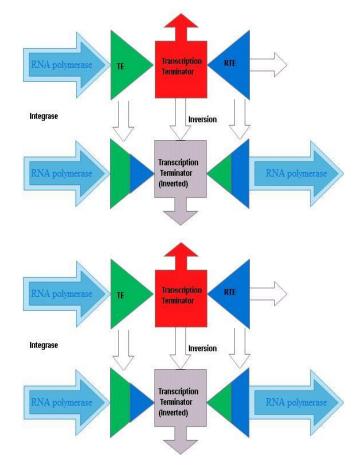

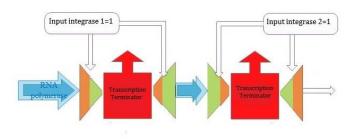

|          | BIO-ELECTRONIC APPROACH FOR VARIOUS ADDERS CIRCUIT                                |             |  |  |  |  |

| IC17EC09 | DESIGN                                                                            |             |  |  |  |  |

|          | E.Ashwini, S.P.Dhivyaa ,A.Daniel Raj,Mr.P.Anil Kumar                              |             |  |  |  |  |

|          | GENETIC ALGORITHM BASED FRACTIONAL ORDER PID                                      |             |  |  |  |  |

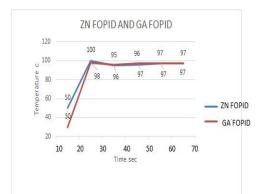

| IC17EC10 | CONTROL FOR TEMPERATURE CONTROL PLANT                                             |             |  |  |  |  |

|          | Dr.G.Sridhar                                                                      |             |  |  |  |  |

|                      | NON-CONVENTIONAL LOW POWER CIRCUIT DESIGN           |     |  |  |  |  |

|----------------------|-----------------------------------------------------|-----|--|--|--|--|

|                      |                                                     |     |  |  |  |  |

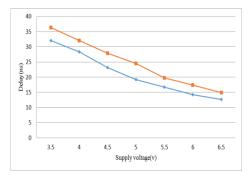

| IC17EC11             | TECHNIQUES                                          | 60  |  |  |  |  |

|                      | N. Raj, P. Anil Kumar, A.K. Singh and P. John Paul  |     |  |  |  |  |

|                      | MOBILITY BASED ENERGY EFFICIENT TRACKING USING      |     |  |  |  |  |

| IC17EC12             | FIREFLY ALGORITHM IN WIRELESS SENSOR NETWORK        | 66  |  |  |  |  |

|                      | Bhuvaneswari.Katikala, Dr.G.Sridhar                 |     |  |  |  |  |

|                      | AN OPEN BOUND ESTIMATOR UNDER CHANNEL DIVERSITY IN  |     |  |  |  |  |

| IC17EC13             | HETEROGENEOUS NETWORK                               |     |  |  |  |  |

|                      | B.Manjula, V.Venkata Rao, P.Chandrasekhar Reddy     |     |  |  |  |  |

|                      | ANALYSIS OF ENERGY EFFICIENT TRACKING IN WIRELESS   |     |  |  |  |  |

| IC17EC14             | SENSOR NETWORKS                                     | 77  |  |  |  |  |

|                      | B.Uma Maheshwari, Dr.G.Sridhar                      |     |  |  |  |  |

|                      | COMBINATION OF IRIS FEATURE AND PALM PRINT FEATURES |     |  |  |  |  |

| IC17EC15             | FOR SECURITY APPLICATIONS                           |     |  |  |  |  |

|                      | A.Suresh Reddy, M.Shiva Kumar                       |     |  |  |  |  |

|                      | DESIGN OF NOISE FREE FILTER FOR SERIAL DATA         |     |  |  |  |  |

| IC17EC16             | COMMUNICATION USING MEJORITY VOTER CONCEPT          |     |  |  |  |  |

|                      | Rajesh Durgam, Thirupathi Durgam                    |     |  |  |  |  |

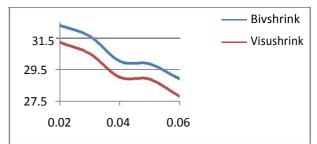

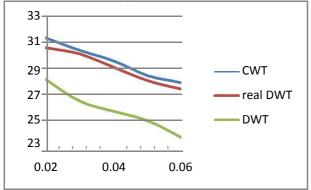

|                      | MEDICAL IMAGE DENOISING USING DUAL-TREE WAVELET     |     |  |  |  |  |

| IC17EC17             | COMPLEX TRANSFORM SHRINKAGE                         |     |  |  |  |  |

|                      | Ayesha Parveen, S.Mahesh                            |     |  |  |  |  |

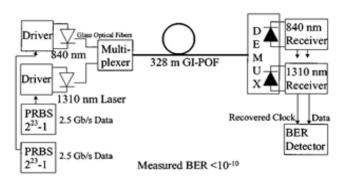

|                      | MULTIMODE GRADED-INDEX POLYMER OPTICAL FIBER FOR    |     |  |  |  |  |

| IC17EC18             | HIGH-CAPACITY LONG HAUL MULTIPLEXED TRANSMISSION    | 104 |  |  |  |  |

|                      | Chandan Kumar Roy, Kishor Krishna Kumar             |     |  |  |  |  |

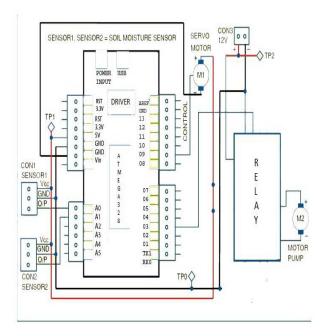

| IC17EC19             | SMART WATER SPRINKLER BASED ON MICROCONTROLLER      |     |  |  |  |  |

|                      | B. Vijaya ,M. Shiva Kumar                           |     |  |  |  |  |

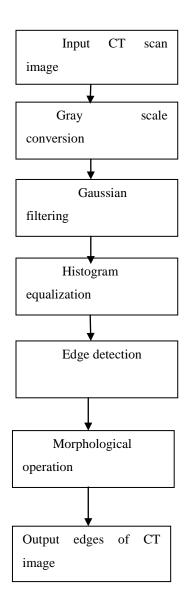

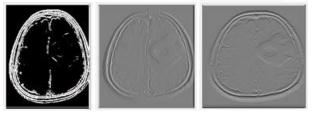

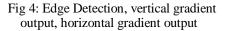

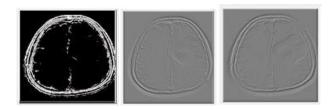

| IC17EC20             | LUNG CANCER DETECTION TECHNIQUES USING GRADIENT     | 115 |  |  |  |  |

| $\alpha_1 / C C 2 U$ | OPERATORS                                           | 115 |  |  |  |  |

|          | G.Naveen, Dr.M.Thamarai                                                                      |     |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------|-----|--|--|--|--|

| IC17EC21 | SEGMENTATION OF BRAIN TUMOUR AFFECTED CELLS USING<br>SIMULINK MODEL                          |     |  |  |  |  |

|          | Vemula Swarnalatha , Dr.M.Thamarai , Dr.K.Sathesh                                            |     |  |  |  |  |

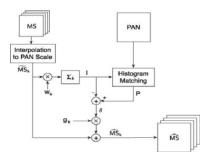

| IC17EC22 | ANALYSIS OF MULTISPECTRAL IMAGE COMPRESSION                                                  | 126 |  |  |  |  |

| ICT/LC22 | Mounika C, Thamarai M, Dhinesh Sharma                                                        | 120 |  |  |  |  |

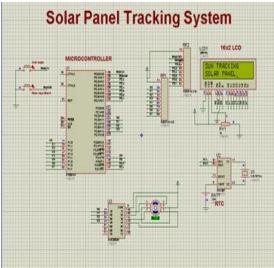

|          | DUAL AXIS SOLAR TRACKER USING MICRONTROLLER                                                  |     |  |  |  |  |

| IC17EC23 | G.Swathi D.Rajendra Prasad                                                                   |     |  |  |  |  |

| IC17EC24 | POWER ESTIMATION AND OPTIMIZATION TECHNIQUES USING<br>VLSI                                   |     |  |  |  |  |

|          | B Ashok K Rajeshwar P.Anilkumar                                                              |     |  |  |  |  |

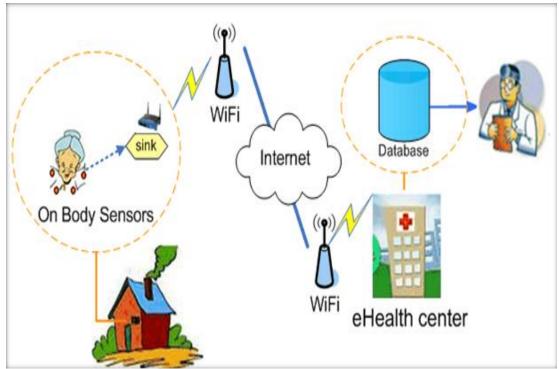

| IC17EC25 | A REVIEW ON HEALTH MONITORING SYSTEM BY WIRELESS<br>SENSOR NETWORK                           |     |  |  |  |  |

|          | Ch. Jyotsna Rani, K. Bhagya Lakshmi, Dinesh Sharma, Purnima K Sharma                         |     |  |  |  |  |

| IC17EC26 | SPATIAL METHODS FOR MULTISPECTRAL PANSHARPENING:<br>DEMYSTIFIED AND MULTIRESOLUTION ANALYSIS |     |  |  |  |  |

|          | M.Lekshmi                                                                                    |     |  |  |  |  |

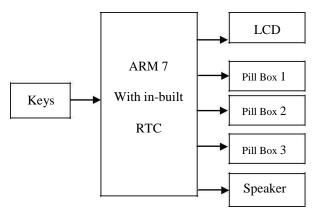

| IC17EC27 | APPLICATIONS OF ARM PROCESSORS IN INDUSTRIES                                                 |     |  |  |  |  |

| ICT/EC2/ | PochamoaniSathyanarayana Yadav , S.P.Aruna , Dr.M. Thamarai, Purnima<br>K Sharma             |     |  |  |  |  |

|          | LOW POWER FAULT TOLERANT ALU                                                                 | 164 |  |  |  |  |

| IC17EC28 | F. Begum and N. Raj                                                                          |     |  |  |  |  |

| IC17EC29 | DESIGN OF AN AREA- EFFICIENT MILLION- BIT INTEGER<br>MULTIPLIER                              | 168 |  |  |  |  |

|          | T. R. Merlin Mishma                                                                          |     |  |  |  |  |

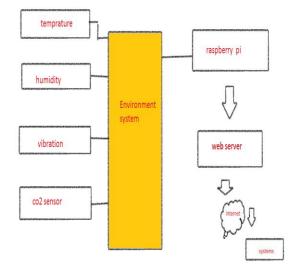

|          | APPLICATION OF RASPBERRY-PI FOR ENVIRONMENT            |     |  |  |  |  |

|----------|--------------------------------------------------------|-----|--|--|--|--|

| IC17EC30 | MONITORING SYSTEM                                      | 172 |  |  |  |  |

|          | Srikonda Shailaja, N. Raj and P. John Paul             |     |  |  |  |  |

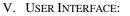

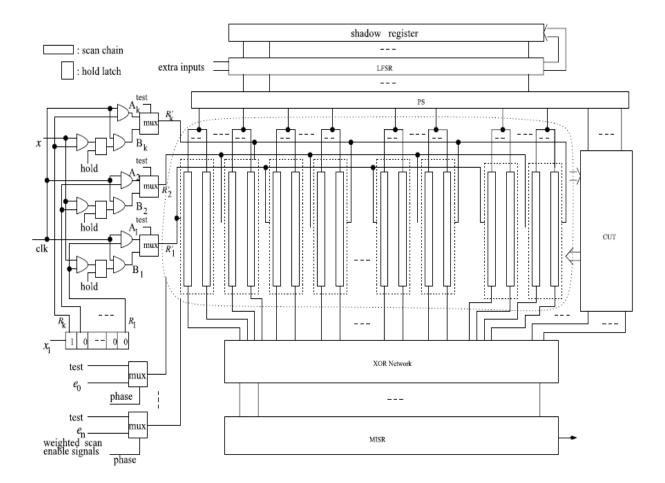

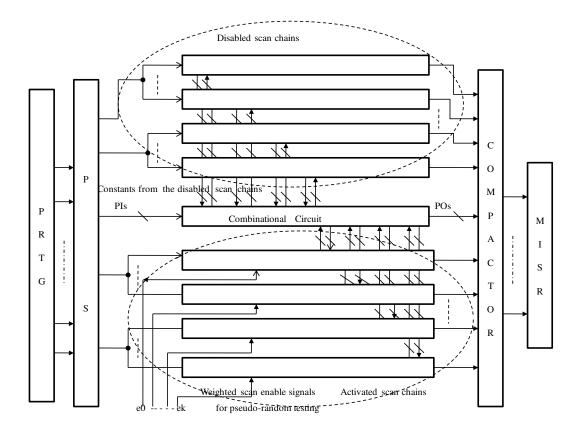

| 10175021 | A NOVEL WEIGHTED SCAN-BASED TEST PATTERN FOR           |     |  |  |  |  |

| IC17EC31 | BUILT-IN SELF-TEST                                     | 176 |  |  |  |  |

|          | D.GaspinBeautly                                        |     |  |  |  |  |

|          | REVERSIBLE ADDER/SUBTRACTOR CIRCUITS: A STUDY          |     |  |  |  |  |

| IC17EC32 | T. Melina, N. Raj and P. John Paul                     | 186 |  |  |  |  |

|          | NOVEL ENERGY EFFICIENT CARRY SKIP ADDER BASED ON       |     |  |  |  |  |

| IC17EC33 | DUAL MODE LOGIC DESIGN                                 | 191 |  |  |  |  |

|          | Ms.C.Aishwarya, Mrs.J.R.Beny, R.Rajasekaran, G.Abirami |     |  |  |  |  |

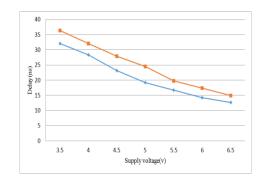

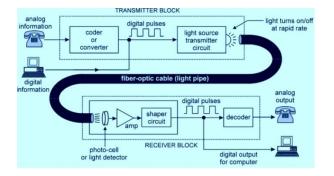

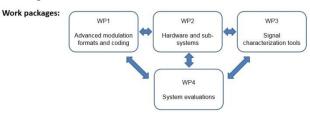

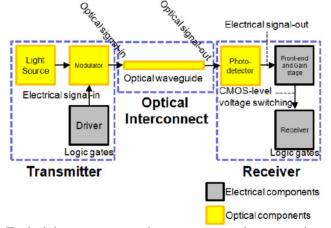

| IC17EC34 | RECENT TRENDS IN OPTICAL COMMUNICATIONS                |     |  |  |  |  |

| ICT/EC34 | Suresh Kumar Perumalla,Dr.G.Sridhar                    |     |  |  |  |  |

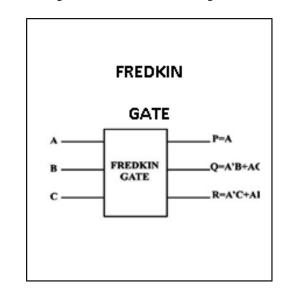

|          | REVERSIBLE GATES FOR DIGITAL DESIGN                    |     |  |  |  |  |

| IC17EC35 | D. Reddy, N. Raj and G. Ahmed                          |     |  |  |  |  |

|          | ANALYZE ON PATH LOSS MODELS OF SPECTRUM SENSING IN     |     |  |  |  |  |

| IC17EC36 | COGNITIVE RADIO NETWORKS                               |     |  |  |  |  |

|          | D.Thirupath, Naga Harika, D.Rajesh                     |     |  |  |  |  |

| IC17EC37 | AREA-AWARE AND SAFER CARDS                             |     |  |  |  |  |

| ICT/EC3/ | T.Mounika, A.Suresh Reddy,M.Shiva Kumar                | 216 |  |  |  |  |

|          | HARD FAULTS AUTO CORRECTION USING FPGA                 | 221 |  |  |  |  |

| IC17EC38 | H. Machaand and N. Raj                                 |     |  |  |  |  |

|          | INEXACT COMPUTING IN DIGITAL SYSTEMS WITH              |     |  |  |  |  |

| IC17EC39 | TRANSMISSION GATE-BASED APPROXIMATE ADDERS             | 225 |  |  |  |  |

|          | K. Swapna and N. Raj                                   |     |  |  |  |  |

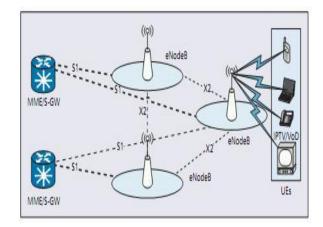

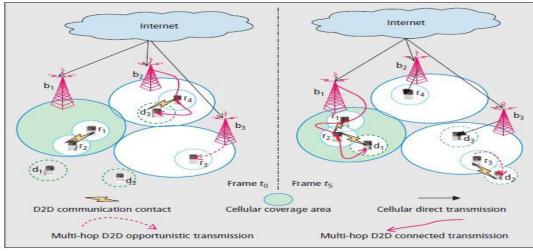

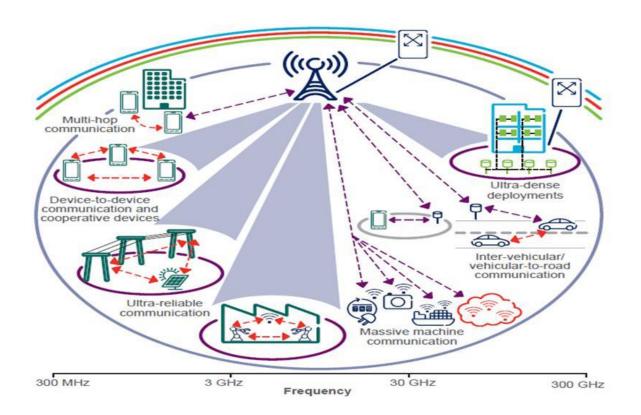

|          | A STUDY ON COMMUNICATION INFRASTRUCTURES IN 5G         |     |  |  |  |  |

| IC17EC40 | CELLULAR NETWORKS                                      |     |  |  |  |  |

|          | M. Suresh M.Thirupathi P.Anilkumar                     |     |  |  |  |  |

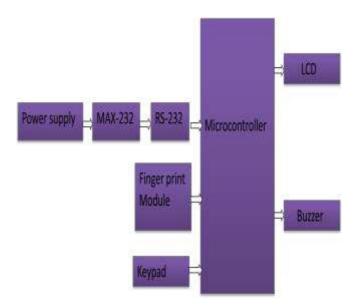

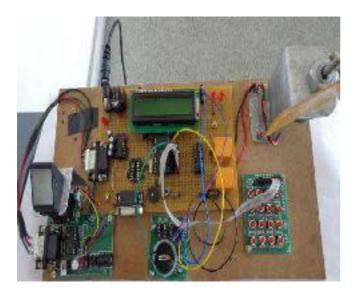

|          | RFID BASED DOOR LOCKING SYSTEM USING FINGER PRINT                            |         |  |  |  |  |

|----------|------------------------------------------------------------------------------|---------|--|--|--|--|

| IC17EC41 | D.Rajendra Prasad, RamarajuHemakavitha                                       |         |  |  |  |  |

|          | IMPLEMENTATION OF WIDEBAND SPECTRUM SENSING FOR                              | 240     |  |  |  |  |

| IC17EC42 | PERFORMANCE IMPROVEMENT OF COGNITIVE RADIO                                   |         |  |  |  |  |

|          | BalaTejavath,K.Kirankumar,P.Venkatapathi                                     |         |  |  |  |  |

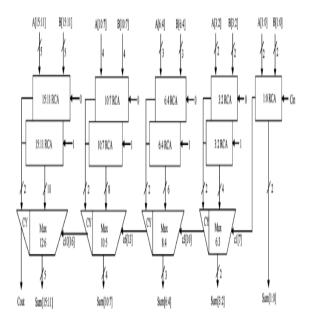

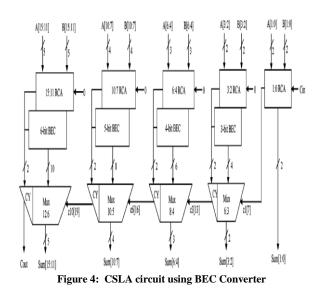

| IC17EC43 | LOW POWER HIGH SPEED CSLA                                                    |         |  |  |  |  |

|          | P. Gupta, N. Raj and P. John Paul                                            | 245     |  |  |  |  |

|          | AN OVERVIEW OF 5G TECHNOLOGY                                                 | 249     |  |  |  |  |

| IC17EC44 | Gowthampolumati , Dr.M.Thamarai                                              | 247     |  |  |  |  |

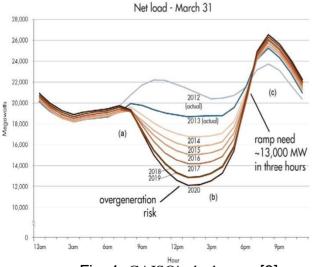

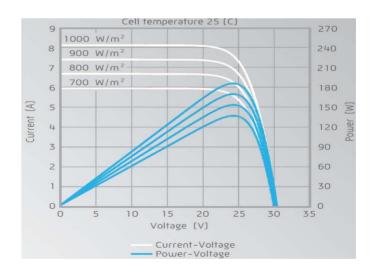

|          | A REVIEW ON TRENDS AND CHALLENGES OF GRIDCONNECTED                           |         |  |  |  |  |

| IC17EC45 | 5 PHOTOVOLTAIC SYSTEMS                                                       |         |  |  |  |  |

|          | DRK Mahesh P Manikyarao                                                      |         |  |  |  |  |

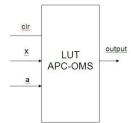

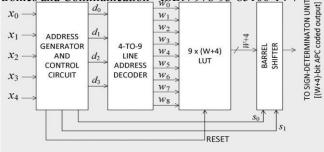

| IC17EC46 | OPTIMIZATION OF LUT FOR MEMORY-BASED COMPUTATION<br>USING APC&OMS TECHNIQUES |         |  |  |  |  |

|          | A.Suresh Reddy, M.Srikanth                                                   |         |  |  |  |  |

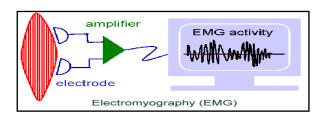

|          | SST WITH EMG BASED NOISE REDUCTION SYSTEM                                    |         |  |  |  |  |

| IC17EC47 | K.ManiKanta P AnilkumarDr.M.Thamarai                                         |         |  |  |  |  |

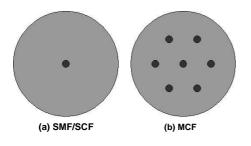

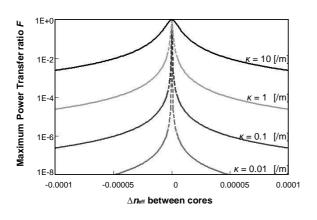

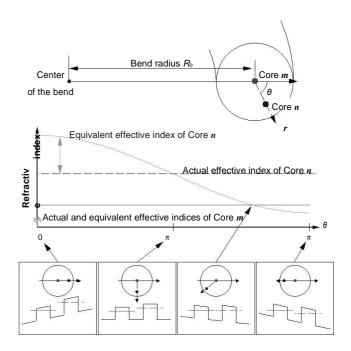

|          | MULTI-CORE FIBER FOR HIGH-CAPACITY LONG-HAUL                                 |         |  |  |  |  |

| IC17EC48 | SPATIALLY-MULTIPLEXED TRANSMISSION                                           | 272     |  |  |  |  |

|          | Chandan Kumar Roy B. Prashanth                                               |         |  |  |  |  |

|          | INDUSTRIAL AUTOMATION CONTROL USING LI-FI<br>TECHNOLOGY                      | • • • • |  |  |  |  |

| IC17EC49 | G.Sonalika, Dr.G.Sridhar                                                     | 280     |  |  |  |  |

|          | THE COMPARISON OF NON-COOPERATIVE SPECTRUM SENSING                           |         |  |  |  |  |

| IC17EC50 | TECHNIQUES FOR PERFORMANCE IMPROVEMENT OF<br>COGNITIVE RADIO                 | 286     |  |  |  |  |

| lei/Lej0 | P.VenkatapathiGudipellyMamathaDr.S.Srinivasa Rao Dr.Habibulla<br>Khan        |         |  |  |  |  |

| IC17EC51 | AUTOMATED IRRIGATION SYSTEM USING<br>MICROCONTROLLER<br>E.Bharani, Sneha Reddy                                                 | 290 |

|----------|--------------------------------------------------------------------------------------------------------------------------------|-----|

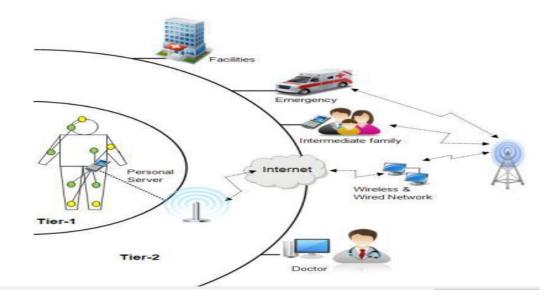

| IC17EC52 | A CASE STUDY ON ULTRA LOW POWER WIRELESS BODY<br>MOUNTED SENSORS FOR HEALTH MONITORING<br>P. AnilKumar,P.Venkatapathi,N.Raj    | 297 |

| IC17EC53 | COOPERATIVE SPECTRUM SENSING IN COGNITIVE RADIO: A<br>REVIEW<br>P.Venkatapathi, D.Naresh,Dr.S.Srinivasa Rao ,Dr.Habibulla Khan | 306 |

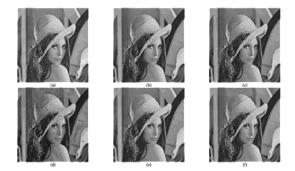

## VIDEO ENHANCEMENT USING CONTRAST LIMITED ADAPTIVE HISTOGRAM EQUALIZATION

B.PRABHAKAR,D.KRISHNAREDDY<sup>\*</sup> Dept. of ECE, JNTUHCES Sultanpur,Sangareddy, Telangana,Inida Dept. of ECE CBIT,Hyderabad,Telangana, India<sup>\*</sup> bprabhakar@jntuh.ac.in, <u>dkreddy@cbit.ac.in</u><sup>\*</sup>

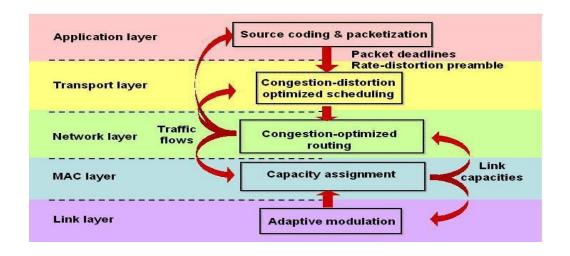

Abstract: With the continuous rise of Internet-based multimedia services, such as video sharing websites, web radios and IP-based telephony, multimedia communications are getting more and more popularity and demand. From the service provider's perspective, there is an increasing need to providing high-quality content; at the same time, from the network provider's view, the requirement is to design networks that can effectively support these services with adequate quality-of-service. Histogram Equalization is a contrast enhancement technique in the image processing which uses the histogram of image. There are several extensions of histogram equalization has been proposed to overcome the brightness preservation. Contrast enhancement using brightness preserving bi-histogram equalization (BBHE) and Dualistic sub image histogram equalization (DSIHE) which divides the image histogram into two parts based on the input mean and median respectively then equalizes each sub histogram independently. Measure video quality by peak signal to noise ratio (PSNR).The purpose of image enhancement is to increase image visibility and details. Enhanced image provide clear image to eyes or assist feature extraction processing in computer vision system.This paper focuses on enhancing the quality of low-grade video of surveillance cameras.

#### Key Words: Histogram Equalization, Contrast Enhancement, Image, MSE, PSNR

#### I. INTRODUCTION

Video enhancement is one of the most important and difficult components in video research. The aim of video enhancement is to improve the visual appearance of the video, or to provide a "better"transform representation for future automated video processing, such as analysis, detection, segmentation, recognition, surveillance, traffic, criminal justice systems. In this paper, we present an overview of video enhancement processing and analysis algorithms used in these applications.

Video enhancement problem can be formulated as follows: given an input low quality video and the output high quality video for specific applications. How can we make video more clearer or subjectively better digital video has become an integral part of everyday life. It is well-known that video enhancement as an active topic in computer vision has received much attention in recent years. The aim is to improve the visual appearance of the

"better"transform video. or to provide а automated video representation for future processing, such as analysis, detection, segmentation, and recognition. Moreover, it helps analyses background information that is essential to understand object behavior without requiring expensive human visual inspection [6]. There are numerous applications where digital video is acquired, processed and used, such as surveillance, general identity verification, traffic, criminal justice systems, civilian or military video processing.

#### II.BRIGHTNESS PRESERVING BI

#### HISTOGRAM EQUALIZATION

The Brightness preserving bi histogram equalization firstly decomposes an input image into two sub images XL and XU based on the mean Xm of the input image. One of the sub image is set of samples less than or equal to the mean whereas the other one is the set of samples greater than the mean. Then the BBHE equalizes the sub images independently based on their respective histograms with the constraint that the samples in the formal set are mapped into the range from the minimum gray level to the input mean and the samples in the latter set are mapped into the range from the mean t the maximum gray level. Means one of the sub images is equalized over the range up to the mean and the other sub image is equalized over the range. From the mean based on the respective histograms. Thus, the resulting equalized sub images are bounded by each other around the input mean, which has an effect of preserving mean brightness.

$X=X_LUX_U$  (1)

Where,  $X_L = \{X(i,j) \mid X(i,j) \le X_m \forall X(i,j) \in X\}$  (2)

And  $X_U = \{X(i,j) \mid X(i,j) > X_m \forall X(i,j) \in X\}$ (3)

The histograms created from  $X_L$  and  $X_U$  are denoted as  $h_L$  and  $h_U$  respectively

Local maximum values of  $h_L(x)$  and  $h_U(x)$  are found by applying differential operation to  $h_L(x)$  and  $h_U(x)$  as shown in equation (4) and (5);

$$h'_{L}(x) = h_{L}(x) \cdot h_{L}(x \cdot 1), \qquad \text{for } 1 \le x \le J$$

(4)

$$h'_{U}(x) = h_{U}(x) - h_{U}(x-1), \quad \text{for } 1 \le x \le J$$

(5)

A sub-congregation  $\{hL(xi)\}$  or histogram local maximum values hL(xi), are found by using the equations (6) and (7);

$$|h'_{L}(x)| < \min\{|h'_{L}(x-1)\rangle|, |h'_{L}(x+1)\rangle|\}$$

(6)

$$h'_{L}(x-1) > 0, h'_{L}(x+1) < 0$$

(7)

Where,  $0 \le x \le J$ ,  $1 \le i \le N_{Lmax}$  and  $N_{Lmax}$  is the number of local maximum values. Mean  $h_{Lk}$ , is derived from sub-congregation  $\{ h_L(x_i) | k \le i \le N_{Lmax} \}$ .

Then, the evaluated  $h_{Lk}$  is the plateau threshold value(i.e.  $T_L$ ) for first sub-histogram and same procedure isfollowed for another sub-histogram and finds  $T_U$ . Thethreshold values of sub-histograms  $h_L$  and  $h_U$  are  $T_L$  and  $T_U$  respectively.

The sub-histograms are modified using threshold operation as shown in equation (8) and (9). The modified histogram  $h_{mod}(x)$  with the threshold value is,

$$\begin{aligned} h_{Lmod}\left(x\right) &= \begin{cases} h_{L}\left(x\right), & \text{for}h_{L}\left(x\right) \leq T_{L}\\ T_{L}, & \text{otherwise} \end{cases} \\ h_{Umod}\left(x\right) &= \begin{cases} h_{U}\left(x\right), & \text{for}h_{U}\left(x\right) \leq T_{U}\\ T_{U}, & \text{otherwise} \end{cases} \end{aligned}$$

Probability Density Functions (PDF's) are found from  $h_{Lmod}(x)$  and  $h_{Umod}(x)$  and then cumulative density functions (CDF)[9].

#### III CONTRAST LIMITED ADAPTIVE HISTOGRAM EQUALIZATION (CLAHE)

Adaptive histogram equalization is a computer image processing technique used to improve contrast in images. It differs from ordinary histogram equalization in the respect that the adaptive method computes several histograms, each corresponding to a distinct section of the image, and uses them to redistribute the lightness values of the image. Ordinary histogram equalization simply uses a single histogram for an entire image.

Consequently, adaptive histogram equalization is considered an image enhancement technique capable of improving an image's local contrast, bringing out more detail in the image.

However, it also can produce significant noise. A generalization of adaptive histogram equalization limited adaptive histogram called contrast as CLAHE, equalization, also known was developed to address the problem of noise amplification. CLAHE operates on small regions in the image, called tiles, rather than the entire image. Each tile's contrast is enhanced, so that the histogram of the output region approximately the histogram specified by matches the 'Distribution' parameter. The neighboring tiles are then combined using bilinear interpolation to eliminate artificially induced boundaries. The contrast, especially in homogeneous areas, can be limited to avoid amplifying any noise that might be present in the image.

Contrast Limited AHE (CLAHE) differs from ordinary adaptive histogram equalization in its contrast limiting. This feature can also be applied to global histogram equalization, giving rise to contrast limited histogram equalization (CLHE), which is rarely used in practice. In the case of CLAHE, the contrast limiting procedure has to be applied for each neighborhood from which a transformation function is derived. CLAHE was developed to prevent the over amplification of noise that adaptive histogram equalization can give rise to.

This is achieved by limiting the contrast enhancement of AHE. The contrast amplification in the vicinity of a given pixel value is given by the slope of the transformation function. This is proportional to the slope of the neighborhood cumulative distribution function (CDF) and therefore to the value of the

histogram at that pixel value. CLAHE limits the amplification by clipping the histogram at a predefined value before computing the CDF. This limits the slope of the CDF and therefore of the transformation function. The value at which the histogram is clipped, the so-called clip limit, depends on the normalization of the histogram and thereby on the size of the neighborhood region. Common values limit the resulting amplification to between 3 and 4 times the histogram mean value.

#### IV. QUALITY ASSESSMENT

It used by many researchers. PSNR is the ratio between the maximum possible power of a signal and the power of corrupting noise that affects the fidelity of its representation. It is defined via the Mean Squared Error (MSE) between an original frame o and the distorted framed as following

$$MSE = \frac{1}{M.N} \sum_{m=1}^{M} \sum_{n=1}^{N} |o(m,n) - d(m,n)|$$

(10)

Where each frame has  $M \times N$  pixels, and o(m, n)and d(m, n) are the luminance pixels in position (m, n) in the frame. Then, PSNR is the logarithmic ratio between the maximum value of a signal and the background noise (MSE). If the maximum luminance value in the frame is L (when the pixels are represented using 8 bits per sample, L = 255) then

$$PSNR = 10 \log \frac{255^2}{MSE}$$

(11)

It can be noticed that PSNR can be computed only once the image is reconstructed at the receiver, hence, it may not be appropriate to use in real-time mechanisms. This is one disadvantage of such metric. The other would be the reliability to derive MOS from this metric. However, according to [5] there exist heuristic mappings of PSNR to MOS as shown in Table 1.

#### Table 1.PSNR and MOS

| •            |

|--------------|

| MOS          |

| 5(Excellent) |

| 4(Good)      |

| 3(Fair)      |

| 2(Poor)      |

| 1(Bad)       |

|              |

#### V.VIDEO ENCHANCEMENT

Video enhancement problem can be formulated as follows: given an input low quality video and the output high quality video for specific applications. How can we make video more clearer or subjectively better. Digital video has become an integral part of everyday life. It is well-known that video Enhancement as an active topic in computer vision has received much attention in recent years. The aim is to improve the visual appearance of the "better" video, or to provide а transform representation for future automated video processing, such analysis, detection. as segmentation, and recognition. Moreover, it helps analyses background information that is essential to understand object behavior without requiring expensive human visual inspection [6]. There are numerous applications where digital video is acquired, processed and used, such as surveillance, general identity verification, traffic, criminal justice systems, civilian or military video processing.

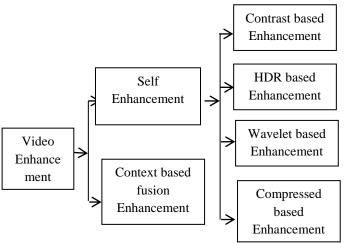

In this paper, if enhanced video embed high quality background information, the existing techniques of video enhancement can be classified into two broad categories: Self-enhancement and frame-based fusion enhancement. Traditional methods of video enhancement are to enhance the low quality video itself. It doesn't embed any high quality background information. Such as contrast enhancement method. HDR-based video compressed-based enhancement. video enhancement, and wavelet-based transform video enhancement. These approaches are uniformly

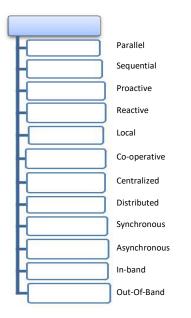

called self-enhancement of low quality video. It don't enough luminous of low quality video. The reason is that in the dark video, some areas are so dark that all the information is already lost in those regions. No matter how much illumination enhancement you apply, it will not be able to bring back lost information. Frame-based fusion enhancement refers to low quality video, which fuse illumination information in different time video. The approach is that it is by extracting high quality background information to embed low quality video. How would one combine information from two (or more) background images in a meaningful way? How would one pick high-quality background parts while keeping all the low-quality important information. To these problems, the previous researchers have abundant research. Fig.1 shows the more detail categories of video enhancement

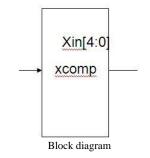

Figure 1: Blok diagram of Video Enhancement

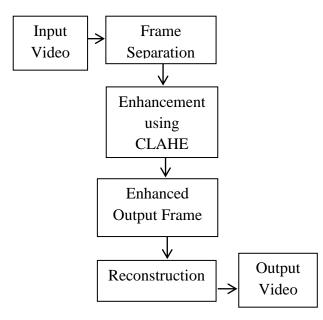

In the frame work show that initially video is first convert into frames and each frame is enhanced by using adaptive histogram equalization process with fusion and red channel processing concept. At the end finally enhanced video we get.

This method is considered a local operator since the operation only affects pixel values in an image individually on a pixel-by-pixel basis and each pixel is mapped in the same way. The global are independent of local spatial context. It performs the same operation on each pixel and don't work well when illumination varies locally. The simplest tone reproduction is a linear mapping which scales the radiances to the range between 0 and 255. The logarithm of the radiances is taken and linearly scaled to [0, 255].

Figure2:Flow diagram of Video Enhancement using CLAHE.

Some regions of a video catch human visual attention at first glance more than other regions, and the regions are considered more salient method.

#### A Framework Overview

Global contrast enhancement is required to reveal hidden details in dark and bright regions. In addition to enhancing regions with extremely high or low luminance, proposed technique is also significantly stretches the contrast in mid-tone regions, which most other curve-based global .Saliency values can be regarded as complex local information indicating the degree of human interest in each pixel in a video. Saliency maps are most frequently used to extract useful objects in the preprocessing of surveillance systems or recognition problems [10].

#### VI. EXPERIMENT RESULTS

In this paper we are using MATLAB Software .MATLAB has evolved over a period of

vears with input from many users. In university environments, it is the standard instructional tool introductory and advanced courses for in mathematics, engineering, and science. In industry, MATLAB is the tool of choice for highproductivity research. development, and analysis.MATLAB features a family of applicationspecific solutions called toolboxes. Very important to most users of MATLAB, toolboxes allow you to learn and apply specialized technology. Toolboxes are comprehensive collections of MATLAB functions (M-files) that extend the MATLAB environment to solve particular classes of problems. Areas in which toolboxes are available include signal processing, control systems, neural networks, fuzzy logic, wavelets, simulation, and many others.

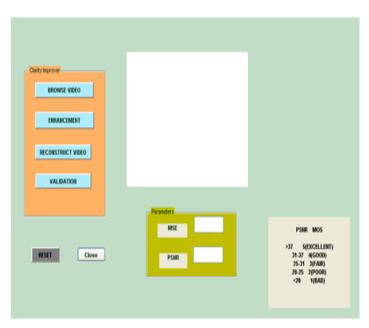

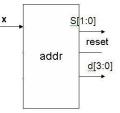

To enhance the better quality of a video the tone adjustment technique is used here. In addition, noise estimation is taken into account to quantify the artifacts of noise generation during contrast enhancement process. The Video sequence is separated into frames to yield a single high quality image.Fig 3 is shows the paper proposed technique front panel and it implement using MATLAB 7.11 Version its show the GUI of the paper.

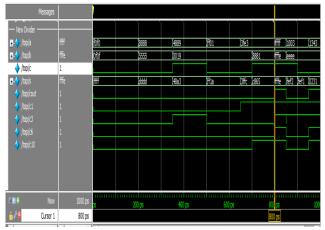

Figure 3:.GUI of Video enhancement Technique

GUI is consists of four Push Bottons they are Browse Video, Enhancement, Reconstruction and Validation.

When Browse Video button is pressed below window display and selected video is played.

Figure4: Video Browse push button window

When Enhancement push button is pressed this below window appears. Enhancement process is started first separating frame and enhancement is done.

Figure5: separating frames window

After separating enhancement is done my using AHE with fusion and red channel processing

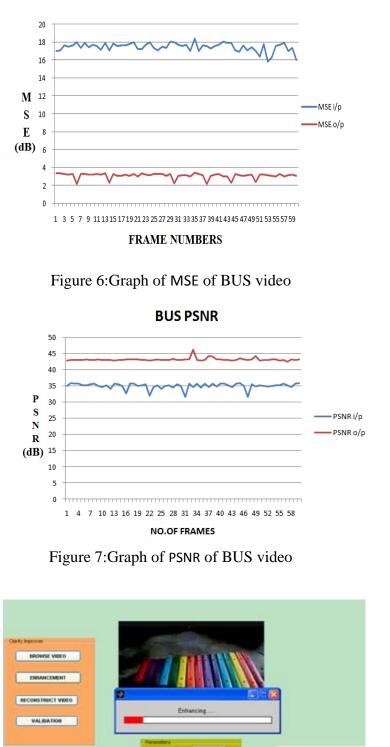

**BUS MSE**

Figure 8: enhancing frames window

RESET

Close

Proceedings of International Conference on Latest Trends in Electronics and Communication - ISBN 978-93-85100-14-7

After enhancing again enhanced video is played so that enhancement can be observed.

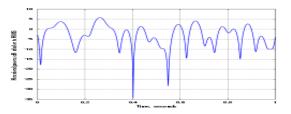

Figure9: Enhanced video is playing window After enhancing for the purpose of video quality estimation calculating PSNR of video.

Figure 10: MSE & PSNR calculation window

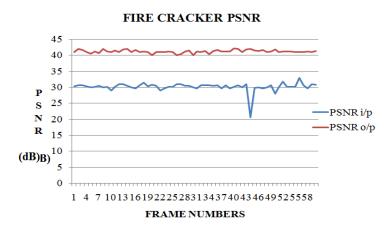

Figure 12:Graph of PSNR of FIRE CRAKER video

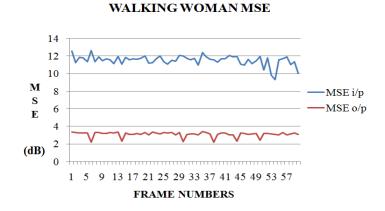

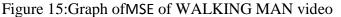

Figure 13:GraphofMSE of WALKING WOMAN video

#### WALKING WOMAN PSNR

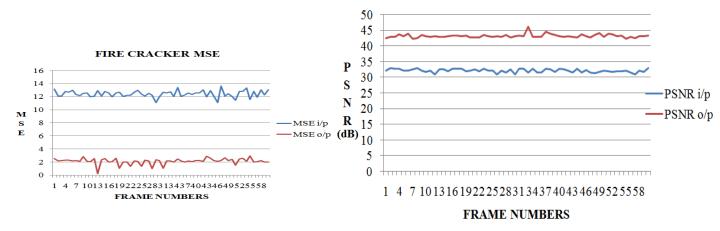

Figure 11: Graphof MSE of FIRE CRAKER video

Figure 14: GraphofPSNR of WALKING WOMAN video

## Figure 16:GraphofPSNR of WALKING WOMAN video

#### VII. CONCLUSION

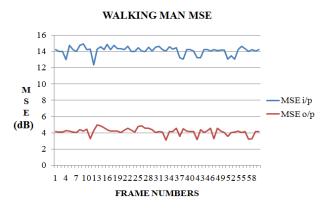

It is observed from the above table 3 the difference in PSNR for Bus video input and output is 8.12 which is a satisfactory result. MSE difference between input and output is 14.16 which is a satisfactory result. It is observed from the above table3 the difference in PSNR for Fire Cracker video input and output is 11.02dB which is a satisfactory result. MSE difference between input and output is 10.29 which is a satisfactory result. It is observed from the above table3 the difference in PSNR for Walking Woman video input and output is 11.04dB which is a satisfactory result. MSE difference between input and output is 8.54 which is a satisfactory result. It is observed from the above table3 the difference in PSNR for Walking man video input and output is 16.45dB which is a satisfactory result. MSE difference between input and output is 9.98 which is a satisfactory result. This proposed video enhancement framework consisting Contrast Limited Adaptive Histogram of Equalization. This work showed that achieves greater performance using luminance component. To evaluate the enhancement performance, the PSNR value was used to measure the quality of enhancement. This technique will also prove that quality of low-grade enhancing the video surveillance cameras.

#### REFERENCES

[1] Journal of Information Hiding and Multimedia Signal Processing Volume 3, Number 1.

[2] KomalVij,Yaduvir Singh Int. J. Comp. Tech. Appl., Vol 2 (2), 309-313

[3]The\_H.264\_advanced\_video\_compression\_stand

[4] Digital Image Processing by R.Gonzalez ,R.Woods.

[5]http://www.any-video-converter.com/mac-

tutorial/video-codec.php.

[6] http://projects.lowtech.org/openmovies/codec.

[7]https://www.videomaker.com/article/c10/15362. [8]https://en.wikipedia.org/wiki/Adaptive histogram equalization.

[9] Satellite Image Contrast Enhancement Algorithm based on Plateau Histogram Equalization,2014 IEEE Region 10 Symposium.

[10] International Journal of Software Engineering and Its Applications Vol.7, No.5 (2013), pp.113-120 http://dx.doi.org/10.14257/ijseia.2013.7.5.11

[11]http://in.mathworks.com/help/images/ref/adapt histeq.html.

[12] Adaptive Clip Limit for Contrast Limited Adaptive Histogram Equalization (CLAHE) Of Medical Images Using Least Mean Square Algorithm.

[13]Histogram Equalization for Image Enhancement Using MRI brain images.

[14] Modified Histogram Based Contrast Enhancement using Homomorphic Filtering for Medical Images.

[15] Signal & Image Processing: An International Journal (SIPIJ) Vol.4, No.5, October 2013.

| S. | Video                | format | Frame rate | Duration | I/P Video | O/P Video | I/P          | O/P          |

|----|----------------------|--------|------------|----------|-----------|-----------|--------------|--------------|

| No | Name                 |        | (f/sec)    | (sec)    | PSNR(dB)  | PSNR(dB)  | Video<br>MSE | Video<br>MSE |

| 1  | Bus                  | .avi   | 15         | 4        | 35.01     | 43.13     | 17.46        | 3.10         |

| 2  | Fire<br>cracker      | .avi   | 15         | 4        | 30.16     | 41.18     | 12.43        | 2.14         |

| 3  | Walkin<br>g<br>woman | .avi   | 15         | 4        | 32.11     | 43.15     | 11.52        | 3.10         |

| 4  | Walkin<br>g man      | .avi   | 15         | 4        | 20.24     | 36.69     | 14.14        | 4.16         |

Table 2: Average PSNR and MSE values of different types of I/P & O/P videos for 60 frames of each

#### BIOGRAPHY

and Head of Department of ECE at JNTUHCEJ

Jagtial (Dist.). Presently he is perusing Ph.D in wireless communication. His research interest incude Mobile commonication, video processing,

image processing and communication. Member of professional bodies LMISTE and FIETE

Dr.D.Krishnareddy is Professor in ECE-Dept.,CBIT,Hyderabad. His research interest incude Mobile commonication,GPS and 3G.Member of professional bodies LMISTE,FIETE and MIEEE

## **Optimized Multi-Wavelet Based Image Compression Model for Medical Applications**

S.Jagadeesh<sup>1</sup>, Dr.E.Nagabhooshanam<sup>2</sup>

<sup>1</sup>Assoc. Prof., HOD, Dept., of ECE, SSJ Engineering College, Hyderabad, India <sup>2</sup>Professor, Dept., of ECE, CMR Engineering College, Hyderabad, India jaga.ssjec@gmail.com, enb1234@gmail.com

Abstract: Medical image compression has become more important in the medical field, because many hospitals use compression store for routine tracking and follow-up. No compression occupies a lot of memory by which there is a heavy hardware complexity. In order to achieve a memory constraint problems, this paper proposed a new image compression model based on multiwavelet transform and a hybrid Huffman encoder. The proposed approach accomplishes the multi wavelet transform to obtain finer resolution level by which the redundant information reduces more effectively. Further the proposed model also accomplished a feature selection process based on the spectral properties of image. Then the obtained spectral features are processed for encoding through a hybrid Huffman encoder. Various test samples are used for performance evaluation under various scenarios such as varying noise variance and varying bit rate.

*Keywords: Medical image compression, Multiwavelet, Power spectral density, Huffman encode, PSNR, CR.*

#### I. INTRODUCTION

Recently, the compression of medical images has gained a lot of research interest to achieve a reduced storage and bandwidth requirements in systems like PCAs (Picture Archival Communication and Systems) and processing telecommunications. Medical image and compression have become important to medical field. Nowadays, many hospitals around the world use compression to store routinely-made patient images for follow-up and tracking the patient state. Basically image compression techniques can be classified into two categories: lossless and lossy compression techniques. Lossless techniques are applied when data are critical and loss of information is not acceptable. Since the medical imagery carries mot important information, the design of a medical image compression technique should be very careful. Even a less information loss results in a large degradation in the quality of image by which the image directs to a wrong diagnosis. Hence the medical images subjects to lossless compression only. There are various medical image compression techniques. In the area of image coding for medical application [1], multi bit rate [2] applications are emerging. Conventional coding approaches are limited to their application due to network diversity issues. Since the medical images carry most important and huge information, encoding them at very low bit rate will results in the information loss and also gives the low quality medical image reconstruction. If this was viewed through the effect of

channel, it will become worse due to the effect of narrow bandwidth. Several approaches are proposed in earlier for encoding the MRI image data before transmission. However, these approaches obtained better results at high bit rates and shown poor results in the case of low bit rates. This problem can be overcome by encoding the Images in such a way that there will be in compatibility for the encoded bits with lower bit rate.

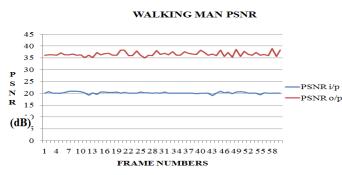

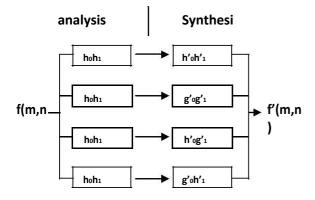

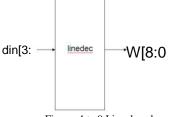

Hierarchical coding is one of the coding techniques which perform image coding in a hierarchical fashion by considering the importance of pixels at every stage. In hierarchical coding, the image is initially processed for decomposition through Discrete Wavelet transform (DWT). DWT decomposes the image into subbands (LL, LH, HL and HH). Then the obtained sub bands are processed for further coding. For the encoding of obtained wavelet bands, various encoding approaches were proposed in past. These coding approaches are lossy or lossless compression approach as per the developed methods. In these approaches more dominantly used approaches are Huffman coding and arithmetic coding approach. As Huffman coding are lower in computational complexity as compared to arithmetic coding mostly Huffman coding are seen in JPEG coding architecture. Huffman coding is entropy based coding technique where the data bits are compressed based on the frequency of occurrence of the unique words. It is often observed that this coding approach allocated higher code bit length than the original code word for lower frequency data bits. This result in decompression and result in higher bit counts. Additionally the decoding states required to decompress the data increases resulting in slower operational speed. To overcome the problems at all phases of image compression system, this work proposed a image compression system based on spectral new characteristics of image. A simple block diagram of the proposed image compression system is shown in figure.1.

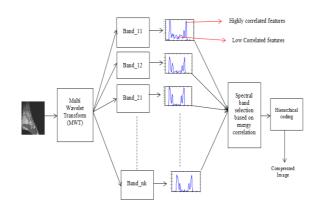

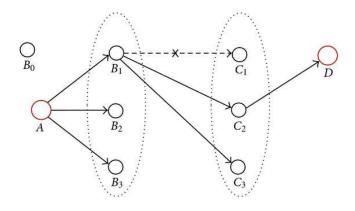

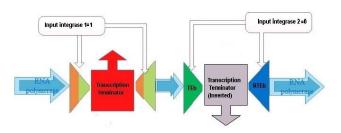

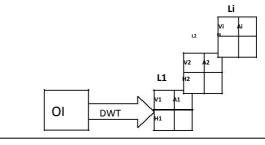

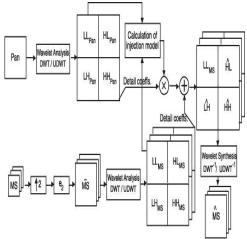

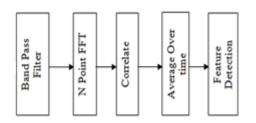

Figure.1 Overall proposed system model

Initially, the image was subjected to multiwavelet transform and then the obtained wavelet bands are subjected to further band coefficient selection process to reduce the additional computational overhead occurred with processing of all wavelet bands. Here the sub band adaptive filtering is accomplished to achieve the bands with less in number. Further the obtained bands are spectral coded based on the correlations between. Then the obtained features are processed for encoding process. To achieve a higher compression and faster decoding time in this work an hybrid coding approach of variable and fixed length coding scheme is to be developed for the improvement of speed and compression ratio for digital image compression.

Rest of the paper is organized as follows: section II illustrates the literature survey. Section III describes the multiwavelet band selection model based on adaptive band filter (ABF). Section IV describes the spectral selective band process. Section V describes the details of proposed hybrid Huffman encoder. Section VI illustrates the experimental results and finally the conclusions are given in section VII.

#### **II. LITERATURE SURVEY**

Recently, in the field of medical image compression, the wavelet transform has been developed as a cutting edge technology. Wavelet-based coding [3], [4], [5], [6] methods provide an improved picture quality at high compression ratios. To achieve the better compression performance, the wavelet filters should have the property of symmetry, orthogonality, higher approximation order and short support. Due to the constraints in the implementation, scalar wavelets can't satisfy all these enhanced properties. Compared with scalar wavelets, Multiwavelets [7], [8], [11] have several advantages and are generated by only a finite set of functions. One of the main advantage with multiwavelet, it can possess symmetry and orthogonality simultaneously [9], [10], whereas the scalar DWT can't possess these two properties simultaneously. These two properties of multiwavelet made it to offer the increased performance and also high degree of freedom compared with scalar wavelets, in image processing applications. Zero-tree/block coding [12], [13], [14], [15] clusters the subband/wavelet coefficients by considering their nature of energies both in space and frequency. These coders apply the hierarchical set partitioning method with respect to a threshold to split the significant coefficients in the bit plane coding pass, while preserving the insignificant coefficients. This procedure creates a symbol by coding large region of zero pixels. This method provides an effective method to represent a group of zeros of subband/wavelet coefficients compactly. The high efficiency in the compression can be achieved through the context modeling [16], [17], [18]. In this type of coders, an arithmetic coding based on the context was applied on the individual pixel of DWT bit planes. In the context modeling, the strong correlations between the coefficients of same band and also with the other bands are utilized effectively for encoding. Though, there is simplicity in the context modeling [13], [14], [15] the limited context information is insufficient to predict the current node's status.

Some carefully designed context modeling algorithms [17], [18] outperformed the zero-tree/block coders in performance with respect to PSNR. However, the computational complexity is observed to be very high, because, there is a need to scan the entire subbnads at least once to complete the encoding of full bitplane.

#### III. BAND SELECTIVE-MULTI WAVELET TECHNIQUE

Here the selective multi-multiwavelet coding is applied over the image to obtain the bands which are more informative instead of all bands. Generally as the band decomposition increases, the probability of redundancy among different bands increases. This redundancy of information increases the processing overhead, and intern makes the system slower. Hence it is required to have an adaptive band selection process for extracting the actual informative band from the processed bands. With reference to band selection process proposed in [19], in this work the process of adaptive band selection is developed for multi wavelet coefficients.

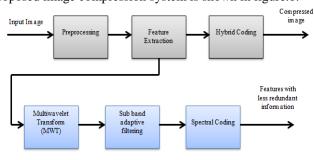

In this process the analysis bank decomposes the image I into K subbands, each produced by a branch  $H_z(k)$  of the analysis bank. After decimation and expansion by a factor N, the full band signal is reconstructed from the subbands in the synthesis bank by filtering with filters  $G_k(z)$  followed by summation. The analysis filters  $H_k(n)$  are derived from the real value of a lowpass FIR filter p[n] of even length L<sub>p</sub>. For the estimation of signal using such filtration cost optimization approach is used where the subband are processed adaptively termed as subband adaptive filter (SAF) [19]. The SAF operation is based on the LMS-type adaptive filter. The convergence of such filter is based on the optimization of this LMS function, wherein weight functions are used to optimize the mean error. To converge the cost function faster in [20] a Normalized SAF (NSAF) is proposed. In [20], the convergence speed is increased by increasing the number of subband filters while maintaining the same level of steadystate error. However, it suffers from huge complexity when used in adapting an extremely long unknown system. To overcome this problem in [21] a dynamic selection based NSAF (DS-NSAF) scheme is proposed. This approach sorts out a subset of the subband filters contributing to convergence performance and utilizes those in updating the adaptive filter weight. This approach dynamically selects the subband filters so as to fulfill the largest decrease of the successive mean square deviations (MSDs) at every iteration. This approach reduces the computational complexity of the conventional SAF with critical sampling while maintaining its selection performance. The operational approach for the conventional DS-SAF approach [20] is as outlined.

In a SAF system the desired band d(n) that originates from an its lowering band is defined by,

$$d(n) = u(n)W^o + v(n) \tag{1}$$

where  $w^0$  is an unknown column vector to be identified with an adaptive filter, v(i) corresponds to a variance  $\sigma_v^2$  for each band, and u(n) denotes a row input vector with length M defined as;

$$u(n) = [u(n) u(n-1) \dots u(n-M+1)]$$

(2)

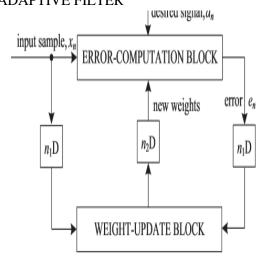

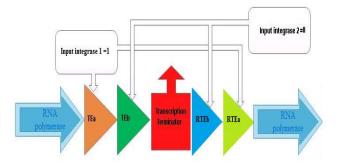

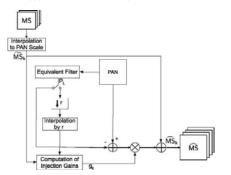

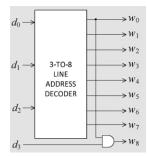

In the process of adaptive selection, the Normalized SAF (NSAF) [21] approach was proposed. A basic architecture for such coding is as shown in figure 2.

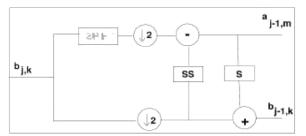

Figure 2. NSAF filter architecture [20]

In this approach the image sample is partitioned into N subbands by the analysis filters  $H_0(z)$ , ...  $H_{n-1}(z)$ . The resulting subband signals are then critically decimated to a lower sampling rate relative to their demanded bandwidth. The original signal d(n) is decimated to k signals and the decimated filter output at each subband is defined as;  $y_{i,D}(k) = u_i(k)w(k)$ , (3)

Where,  $u_i(k)$  is a 1 x M row such that,

$u_i(k) = [u_i(kN), u_i(kN - 1), \dots, u_i(kN - M + 1)]$  and

$w(k) = [w_0(k), w_1(k), \dots, w_{M-1}(k)]^T$  denotes the estimated weight value and the decimated band error is then defined by,

$$e_{i,D}(k) = d_{i,D}(k) - y_{i,D}(k) = d_{i,D}(k) - u_i(k)w(k)$$

(4)

Where  $d_{i,D}(k) = d_i(kN)$  is the reference information at each band. In the process of NSAF the weight optimization is defined as,

$$w(k+1) = w(k) + \mu \sum_{i=0}^{N-1} \frac{u_i^T(k)}{\|u_i(k)\|^2} e_{i,D}(k)$$

(5)

Where  $\mu$  is the step size.

This weight is used to optimize the band selection process where in it takes a large computation to converge for the optimization. To overcome this issue in [20] a MSD based weight optimization is proposed. In this DS-NSAF approach the largest decrease of the MSDs between successive iterations is used.

Hence the weight error vector is then defined as,  $\tilde{w}(k) = w^o - w(k)$ . The weight optimization is then defined as,

$$\widetilde{w}(k+1) = \widetilde{w}(k) - \mu \sum_{i=0}^{N-1} \frac{u_i^I(k)}{\|u_i(k)\|^2} e_{i,D}(k)$$

(6)

Using this weight vector and taking the expectation a MSD is computed which satisfies the absolute expectation as,

$$E \|\widetilde{w}(k+1)\|^{2} = E \|\widetilde{w}(k)\|^{2} + \mu^{2}E \left[\sum_{i=0}^{N-1} \frac{e_{i,d}^{i}(k)}{\|u_{i}(k)\|^{2}}\right] - 2\mu E \left[\sum_{i=0}^{N-1} \frac{u_{i}(k)\widetilde{w}(k)e_{i,D}(k)}{\|u_{i}(k)\|^{2}}\right] = (7)$$

$$\triangleq E \|\widetilde{w}(k)\|^{2}$$

Where

$$\Delta = \mu \sum_{i=0}^{N-1} \left( 2E \left[ \frac{u_i(k)\tilde{w}(k)e_{i,D}(k)}{\|u_i(k)\|^2} \right] - \mu E \left[ \frac{e_{i,d}^2(k)}{\|u_i(k)\|^2} \right] \right)$$

(8)

Defines the difference of MSDs between two

Defines the difference of MSDs between two successive bands. With bands having minimum MSD is then chosen to have a selective band for processing rather to all decomposed bands. This band selection process reduces the processing coefficient with minimum deviation due to the selecting criterion of minimum MSD value.

#### **IV. SPECTRAL FEATURES SELECTION**

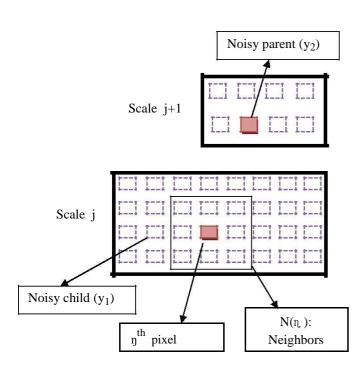

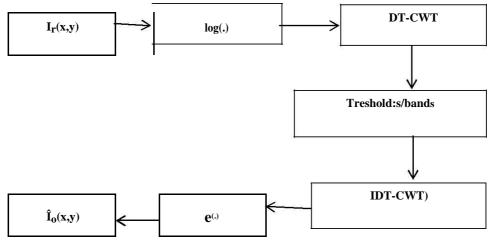

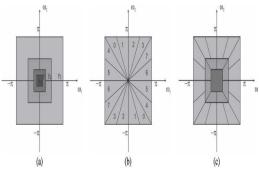

The compression is to be applied on the regions wherein the image is not affected for its visual quality. To achieve a better embedding operation in this work we have applied directional filters which predict the variations in every direction, i.e. the direction in which the coefficient are least variant, is selected for embedding. The region of such distribution is best suitable for embedding as the energy distribution in such region is very low in a particular direction. Hence directional filters based embedding is best suited for compression in spectral domain. To achieve the objective in this work, a spectral selection approach for coefficient selection is developed based on the power spectral density (PSD).

Fig.3 Spectral Feature Selection from the selected bands For the selection of the selective coefficient of the selected spectrum, a coefficient selection algorithm is proposed. The developed approach is termed as "Spectral selective coding" (SSC). The process of selective coding is as outlined; For the selected Normalized band 'BN<sub>i</sub>' obtained from the decomposition approach, a decision of coefficient selection is made based on spectral magnitude. This approach of coefficient selection, results in selection of coefficients, at lower frequency level without effecting higher resolutions coefficients. To compute the spectral magnitude of the band coefficient a power spectral densities (PSD) is computed. PSD is defined as a density operator which defines the variation of power over different content frequencies, in a given signal x(t).

The Power spectral density (PSD) for the given matrix 'x' varying with 't' is defined as,

$$P = \lim_{T \to \infty} \frac{1}{2T} \int_{-T}^{T} B(t)^2 dt$$

(9)

Where B(t) is the band obtained through the multiwavelet decomposition and P is the power spectral density over a time period t. Taking the selected band 'B<sub>Ni</sub>' as reference, a PSD for each coefficient, 'PB<sub>i</sub>' is computed. The PSD coefficients for the normalized band matrix of dimension m x n is defined by,

$$PB_{i,j} = PSD (B_{Ni,j})$$

, for  $i = 1$  to m and  $j = 1$  to n (10)

The PSD per coefficient is defined as,

$$PB_{i,j} = \lim_{T \to \infty} \frac{1}{2T} \int_{-T}^{T} B_{Ni,j}(t)^2 dt$$

(11)

Where, i,j are the corresponding row and column, which are read over a time period of 't'. 't' is the time taken to read the whole set of ' $B_{Ni}$ ' matrix.

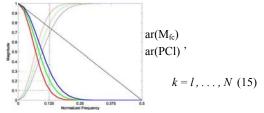

For the obtained power spectral densities of all bands, a correlation factor is measured successively. The correlation is measured for all bands with respect to all bands. i.e., intra bands and inter bands (multi wavelet bands from LL band and the remaining LH, HL and HH bands). The sub bands which having less correlation is selected for further encoding. The bands which have minimum correlation can reduce the redundant information more precisely and also ensures less computational complexity.

#### V. ENTROPY DRIVEN BIT CODING

Two statistical methods of data compression namely Huffman and Hybrid Huffman coding are used here for the compression/ Decompression of medical image. Further analyses on the two methods are carried out with reference to the speed of encoding and decoding, the memory used for the storage of these test sets. The system consists of an encoder block and a decoder block for the compression and decompression of the image considered. Further encoding is processed over the selected features as discussed in section IV. Initially they are transformed into binary format. Ten they are processed for the encoding through the proposed entropy driven coding.

There is a tradeoff in selecting the code between the amount of compression that is achieved and the complexity of the decoder. Moreover, if the clock frequency of the tester is  $f_T$ and the clock frequency of the scan chain is  $f_{\mbox{\scriptsize sys}}$  (system clock frequency) then the ratio of the system clock frequency and the tester clock frequency  $f_{sys}=f_T$  limits the minimum size of a codeword. The compression/decompression scheme described in this paper is based on hybrid Huffman coding. In statistical coding, variable length code words are used to represent fixedlength blocks of bits in a data set. The most popular Huffman code gives the optimum compression for a test set divided into a particular fixed-length block size, it generally requires a very large decoder. A Huffman code for a fixed-length block size of b bits requires a finite state machine (FSM) decoder with 2<sub>b</sub>-1 states. Thus, the size of the decoder for a Huffman code grows exponentially as the block size is increased.

During the time that the contents of the serializer are being shifted into the scan chain, the tester is shifting bits into the decoder. When the decoder receives a complete codeword, it needs to output the corresponding block of b bits into the serializer. If the codeword is too short, then the serializer may not have been emptied yet which would cause a problem for the decoder. So, in order to ensure that the serializer is always empty when the decoder finishes decoding a codeword, the minimum size of a codeword  $L_{min}$  must be no smaller than the ratio of the tester and scan-clock rates times the size of each block,

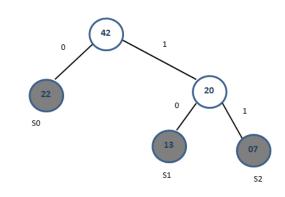

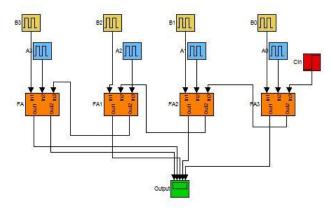

Fig.4 Huffman tree for the three highest frequency symbols

$$L_{min} \ge b \, \frac{f_r}{f_{sys}} \tag{12}$$

For example, if the block size is 8 and the scan-clock rate is twice the tester clock rate, then the minimum size of a code word is 4. Note that if it is not possible to have the scan clock rate be faster, then the tester clock rate, then an alternative solution (as previously described) is to make the scan clock rate be twice as fast as the "effective clock rate" as seen by the decoder by simply having the tester channel feed two scan chains so that the rate that the decoder receives data from the tester is half as fast as the rate at which data can be shifted into the scan chain. Using a Huffman code would provide the maximum compression; however, it would require a complex decoder and may not satisfy the constraint on the minimum size of a codeword. Therefore, some alternative statistical code must be selected. The approach taken here involves using a selective coding approach for which a very simple decoder can be constructed. Consider the case where the test set is divided into fixed-length blocks of b bits. There will be  $2^{b}$  Code words. The first bit of each codeword will be used to indicate whether the following bits are coded or not. If the first bit of the codeword is a 0, then the next b bits are not coded and can simply be passed through the decoder as is (hence, the complete codeword has b + 1 bits).

#### **VI. SIMULATION RESULTS**

The performance evaluation of proposed compression model is described in this section. Various types of medical images like MRI, CT, X-RAY are taken as test samples. For every case of test sample, the proposed model accomplishes compression and decompression and the performance was evaluated through some performance metrics such as Peak Signal to Noise Ratio (PSNR), Mean Square Error (MSE), Computation Time (CT), Processing Overhead and the Compression Rate (CR). The test Sample considered for simulation are represented in figure.5. Matlab software was used to implement the proposed compression model. The obtained results under Gaussian noise variance of 0.01 are shown in the following table.

Figure.5 test samples

Table.1 Observed results for the test samples under noise variance

| Original sample | Noise Added Sample | Retrieved Sample                                      |

|-----------------|--------------------|-------------------------------------------------------|

| Organd Sample   | Neise Addrd Sample | Retioned Sample<br>Retioned Sample<br>Retioned Sample |

|                 | 3                  |                                                       |

| Organi Sample   | Note Added Sample  | Retrieved Sample                                      |

| Crigred Sample  | Noise Addad Sample | Retirend Sample                                       |

| Organi Sanga    | Nase Added Semple  | Retined Sample                                        |

| Original Sample | Noise Addid Sample | Retrieved Sample                                      |

| Dignet Sarpie   | Noise Addrd Sample | Retriend Sample                                       |

| Organit Sample  | Noise Added Sample | Refreed Sample                                        |

The compression performance also depends on the bit rate, i.e bit per pixels. As the bit

per pixels increases, the quality of image retrieved at decoder increases. Thus the proposed approach with higher bit rate has better performance. However as the bit rate increases, the computational time increases. The obtained results under various bit rates are shown in table.2, below.

| Original sample | Retrieved Sample at |                  |                  |                 |  |

|-----------------|---------------------|------------------|------------------|-----------------|--|

|                 | BPP=0.2             | BPP=0.4          | BPP=0.6          | BPP=0.8         |  |

| Crighel Sample  | Retited Surge       | Retried Sangle   | Retineed Sample  | Referent Sample |  |

| Criginal Sample | Retixed Sprey       | Retried Sample   | Retrieved Sample | Release Starpin |  |

| Orgred Sample   | Reticue d'ampie     | Retried Sample   | Retreed Bands    | Refered Supple  |  |

| Cirginal Sample | Relies Sante        | Refered Sample   | Retread Same     | Retered Sample  |  |

| Orgend Sample   | Receil large        | Annual Saryis    | Rational Sample  | Researchange    |  |

| Criginal Sample | Relived Sample      | Retrieved Sample | Raticad Sample   | Release Europe  |  |

| Original Sample | Retreat Longs       | Retried Server   | Remond Sample    | Research Danges |  |

| Organi Sangle   | Retroot Burgh       | Restead Earph    | Rational Sample  | Reserved Sample |  |

To evaluate the quality assessment for the processed data the quality metric of peak signal to noise ratio (PSNR), mean square error (MSE) and spatial similarity index measure (SSIM) is used, tested over different noise density and coding factor. PSNR is most commonly used as a measure

of quality of image test sample .Peak signal-tonoise ratio is defined as a ratio between the maximum possible power of a signal and the power of corrupting noise that affects the fidelity of its representation. PSNR is usually expressed in terms of the logarithmic decibel scale.

$$PSNR(dB) = 10 \log_{10} \left( \frac{I_{peak}^2}{MSE} \right)$$

(13)

Where  $I_{peak}$  is the peak values of the input video. Peak signal to noise ratio is used to evaluate the quality of data after retrieval process. The Mean squared error (MSE) of an estimator is one of the way to quantify the amount by which an estimator differs from the true value of the quantity being estimated. As a loss function, MSE is called squared error loss. MSE measures the average of the square of the error. The error is the amount by which the estimator differs from the quantity to be estimated defined by,

$$MSE = \frac{1}{MXN} \sum (f - \hat{f})^2$$

(14)

Where f is the original image and  $\hat{f}$  is the retrieved image. The SSIM, similarity factor establishes the similarity of pixel intensities between the ground truth test sample and the decoded data, given as, Along with these metrics the performance of Proposed compression model is measured through some more performance evaluation parameters such Compression Rate (CR), Encoding Time (ET), Decoding Time (DT) and Total Time (TT). The obtained performance metrics under different cases of noise variances are shown in the table.3.

Table.3 Performance Metrics under various noise variances

| Sample | Noise variance $= 0.01$ |        |        |         | Noise variance $= 0.03$ |        |        |        |         |         |

|--------|-------------------------|--------|--------|---------|-------------------------|--------|--------|--------|---------|---------|

|        | CR                      | ET     | DT     | TT      | PSNR                    | CR     | ET     | DT     | TT      | PSNR    |

| S1     | 2.8854                  | 6.8845 | 2.5466 | 9.4391  | 56.2341                 | 2.5471 | 6.7412 | 2.4485 | 9.1897  | 54.1432 |

| S2     | 2.7451                  | 6.2358 | 2.8563 | 9.0921  | 57.2145                 | 2.3369 | 6.3325 | 2.6685 | 9.0011  | 55.5421 |

| S3     | 2.3678                  | 7.1258 | 3.4178 | 10.2736 | 58.1234                 | 2.1242 | 7.0028 | 3.1472 | 10.1523 | 56.4235 |

| S4     | 3.2214                  | 7.2235 | 3.3387 | 10.5622 | 56.0014                 | 2.9987 | 7.1247 | 3.2014 | 10.3261 | 53.3385 |

| S5     | 2.9965                  | 6.3385 | 2.8741 | 9.2126  | 58.8742                 | 2.5574 | 6.2358 | 2.5813 | 8.8171  | 56.8752 |

| S6     | 3.0028                  | 6.8564 | 2.5671 | 9.4235  | 57.0067                 | 2.8541 | 6.8654 | 2.4478 | 9.3132  | 55.3145 |

| S7     | 2.8512                  | 5.3874 | 2.0035 | 7.3909  | 55.8954                 | 2.6635 | 5.7438 | 2.1038 | 7.8476  | 53.6632 |

| S8     | 3.1458                  | 6.2285 | 2.8562 | 9.0847  | 56.3217                 | 3.0008 | 6.2547 | 2.7968 | 9.0515  | 52.8547 |

Table.4 Performance Metrics under various Bit Rates (Bit Per Pixels (BPP))

| Sample     | BPP = 0.2 |        |        |        |         | BPP = 0.5 |        |        |        |         |

|------------|-----------|--------|--------|--------|---------|-----------|--------|--------|--------|---------|

|            | CR        | ET     | DT     | TT     | PSNR    | CR        | ET     | DT     | TT     | PSNR    |

| S1         | 3.2254    | 6.3312 | 3.0245 | 9.3557 | 58.2278 | 3.5568    | 6.7845 | 3.2254 | 10.009 | 59.3314 |

| S2         | 3.4578    | 6.8745 | 3.1247 | 9.9992 | 59.6978 | 3.8741    | 6.9986 | 3.3369 | 10.335 | 59.8975 |

| <b>S</b> 3 | 3.2689    | 6.3598 | 3.6985 | 10.058 | 58.4478 | 3.5328    | 6.6632 | 3.8654 | 10.528 | 59.1278 |

| S4         | 3.4589    | 7.0021 | 3.2457 | 10.247 | 57.4586 | 3.8657    | 7.3247 | 3.4475 | 10.772 | 58.9687 |

| S5         | 3.0058    | 6.4589 | 3.8852 | 10.344 | 56.3242 | 3.4412    | 6.5879 | 3.9687 | 10.556 | 58.2201 |

| S6         | 3.2568    | 7.2231 | 3.4752 | 10.698 | 56.3324 | 3.4568    | 7.3320 | 3.7542 | 11.086 | 58.1453 |

| <b>S</b> 7 | 3.7742    | 5.9986 | 3.5471 | 9.5457 | 58.2475 | 3.9964    | 6.3254 | 3.7145 | 10.039 | 59.2274 |

| S8         | 3.6539    | 5.9863 | 3.1287 | 9.1152 | 57.3328 | 3.7249    | 6.2289 | 3.2278 | 9.9538 | 59.0028 |

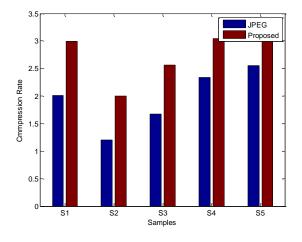

Table.5 comparitive analysis between the proposed and standard JPEG compression

| Metric | S1      |          | S       | 2        | <b>S</b> 3 |          | S4      |          |

|--------|---------|----------|---------|----------|------------|----------|---------|----------|

|        | JPEG    | Proposed | JPEG    | Proposed | JPEG       | Proposed | JPEG    | Proposed |

| CR     | 2.0156  | 2.9956   | 1.2031  | 1.9985   | 1.6719     | 2.5685   | 2.3358  | 3.0417   |

| ET     | 5.2188  | 6.3245   | 4.6406  | 6.4523   | 5.2520     | 6.8885   | 6.8957  | 7.1458   |

| DT     | 9.4063  | 4.2250   | 7.2188  | 4.8795   | 9.7656     | 7.2147   | 9.8886  | 4.8874   |

| TT     | 14.625  | 10.5465  | 11.8594 | 11.3498  | 15.0153    | 14.1302  | 16.7843 | 12.0332  |

| PSNR   | 39.8869 | 45.8635  | 42.5901 | 48.5278  | 39.5556    | 44.7898  | 39.7456 | 46.3289  |

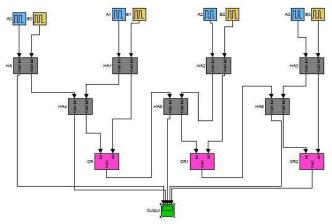

From the table.5, it can be observed that the all performance metrics for the proposed copression model is optimal compared with standard JPEG, expect encoding time. since the proposed approach accomplishes the multiwavelet transform for featureextraction, the time talen for encoding is high. The proposed approach is based on the multiwavelet transform wheres as the JPEG is based on the Discrete wavelet transform. The proposed approach selects the bands followed by feature form the selected bands in an iteratiuve fashion. This phase consumes more time. thus the encoding time for the proposed approahc is obsreved as high compared to JPEG. Except encoding the remaining paramatere such as compression ratio, docidn gtime, total time and

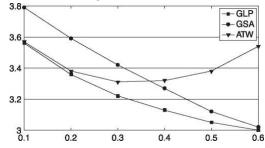

PSNR of proposed approach is observed as optimal compared with JPEG. The repestive compraision plots for compression ratio, total time and PSNR are represented in figure.6, figure.7 and figure.8 respectively.

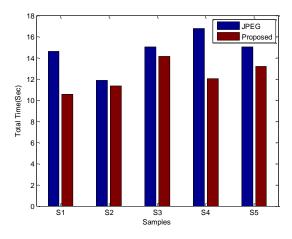

Figure.7 Total time taken in seconds comparision

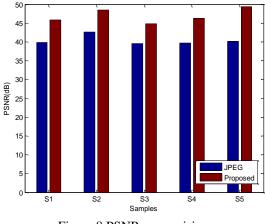

Figure.8 PSNR comparision

From the above figures, it can be observed that the proposed approach has high compression ratio, lower total time an dhigher PSNR. It can also be observed that the proposed approach works effectively even under noise contamination. Thus the proposed compression model achives an optimal performance for medical image compression.

#### VII. CONCLUSION

This paper proposed a new image compression model based multiwavelt transform and the hybrid huffmal coder. The multiwavelet transform helps in searching the more and more finer resolution levels in which the image wont be effected during the compression. For the obtaine multiwavelet bands, a feature selection process is applied to further reduce the redundant information based on the spectral properties. Further the obtained features are processed for encoding through the proposed hybrid hufmann encoder. The simulation results illustraes the performance of approach and outperforms proposed the conventional approach both visually and numerically.

#### **VIII. REFERENCES**

[1] Stephen Wong et al, "Radiologic Image Compression – AReview", IEEE Trans. On Medical Imaging, vol 83, Febraury1995.

[2] Lalitha Y. S, "Image Compression of MRI Image using Planar Coding", (IJACSA) International Journal of Advanced Computer Science and Applications, Vol. 2, No. 7, 2011.

[3]B.Nassiri, R.Latif, "Study of Wavelet Based Medical Image Compression Techniques", International Journal of Engineering Science and Innovative Technology (IJESIT) Volume 3, Issue 3, May 2014.

[4] S. M. Ramesh, Dr. A. Shanmugam, "Medical Image Compression using Wavelet Decomposition for Prediction Method", International Journal of Computer Science and Information Security, Vol. 7, No. 1, 2010.

[5] Anuja P Parameshwaran, Manisha Gaonkar, "DCT and DWT in Medical Image Compression", International Journal on Advanced Computer Theory and Engineering, Volume-2, Issue-3, 2013.

[6] Neha S. Kordel, A. A. Gurjar, "Wavelet Based Medical Image Compression for Telemedicine Application", American Journal of Engineering Research (AJER), Volume-03, Issue-01, 2012.

[7] E. Praveen Kumar, M.G.Sumithra, "Medical Image Compression Using Integer Multi Wavelets Transform For Telemedicine Applications", International Journal Of Engineering And Computer Science, Volume 2 Issue 5 May, 2013.

[8] N.Thilagavathi, K.Subramani, "Medical Image Compression Using Multiwavelet Transform", IOSR Journal of Electronics and Communication Engineering (IOSRJECE), Volume 1, Issue 1 May-June 2012.

[9] Strela V., Heller P., Strang G., Topiwala P., and Heil Ch., "The Application of Multiwavelet Filter Banks to Image Processing," IEEE Transactions on Image Processing, Georgia Institute of Technology, Atlanta, 2002.

[10] Yang Shouzhi, "A Fast Algorithm for Constructing Orthogonal Multiwavelets", Australian Mathematical Society 2004.

[11] K.R. Jayanthi, A. Hazrathaiah, "Multi Wavelet Based Image Compression for tele medical Applications", Advanced Research in Electrical and Electronic Engineering, Vol 1, No.1, 2014.

[12] A. Said Pearlman, "A new, fast, and efficient image codec based on set partitioning in hierarchical trees," IEEE Trans. Circuits Syst. Video Technol., vol.6, no.3, pp.243-249, 1996. [13] D.Taubman, "High Performance scalable image compression with EBCOT", IEEE Trans. Image processing, vol.9, no.7, pp. 1158-1170, 2000.

[14] M.Rabbani and R.Joshi, "An overview of the JPEG 2000 still image compression standard", Signal Processing: Image Communication, vol.17, no.1, pp.3-48, 2002.

[15] S.-T. Hsiang and J.W.Woods, "Embedded image coding using zero blocks and of subband/wavelet coefficients and context modeling", Proc. IEEE ISCAS'00, vol.3, pp. 662-665, Geneva, Switzerland, may 2000.

[16] J.M. Shapiro, "Embedded image coding using zero trees of wavelet coefficients", IEEE Trans. on signal processing.vol.41, pp. 3445-3462. Dec.1993.

[17] G.K. Wallace, "The JPEG still picture compression standard", Communications of the ACM, vol. 34.pp.30-44.April 1991. [18] W.P. Pennebaker and J.L. Mitchell. JPEG Still Image Data Compression Standard. New York: Van Nostrand Reinhold

[19] Kong Aik, Woon Seng Gan Nanyang ,Sen M. Kuo, "Subband Adaptive Filtering Theory and Implementation", John Wiley and Sons, Ltd, 2009.

[20] Moon-Kyu Song, Seong-Eun Kim, Young-Seok Choi, and Woo-Jin Song, "A Selective Normalized Subband Adaptive Filter Exploiting an efficient subset of Sub bands", EURASIP, 2011.

[21] Mohammad Shams Esfand Abadi, and Mohammad Saeed Shafiee, "A New Variable Step-Size Normalized Subband Adaptive Filter Algorithm Employing Dynamic Selection of Subband Filters", IEEE,2013.

## A Framework for Underwater Image Enhancement and Object Detection

<sup>1</sup>Thamarai M , <sup>2</sup>Dhivyaa S P

<sup>1</sup> Professor, Department of ECE, Malla Reddy College of Engineering, Hyderabad, India. <sup>1</sup>mthamarai2014@gmail.com <sup>2</sup>System Analyst, DXC Technology, Bangalore

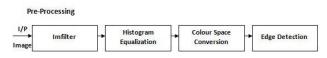

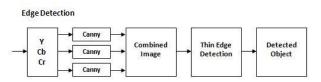

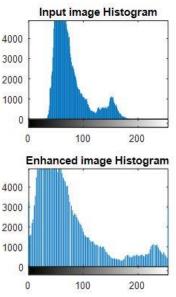

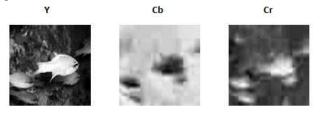

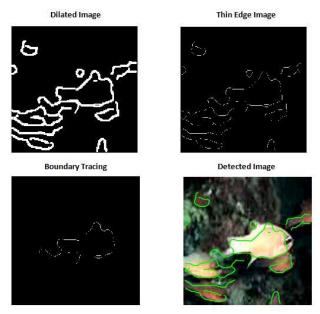

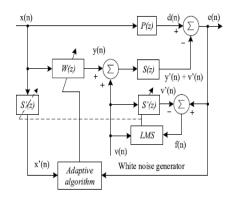

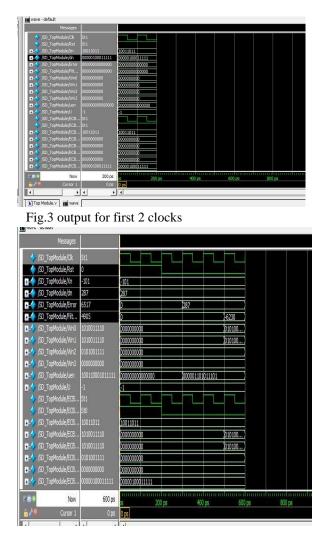

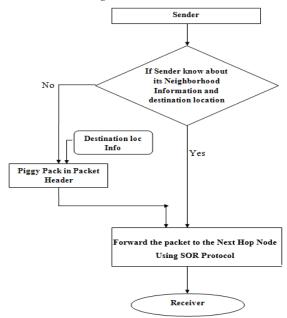

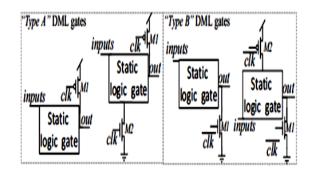

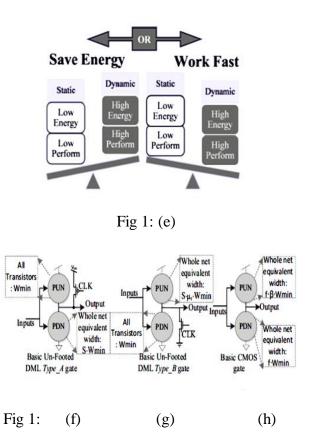

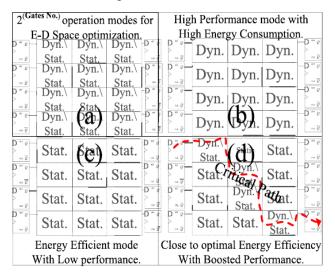

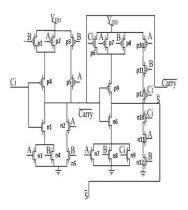

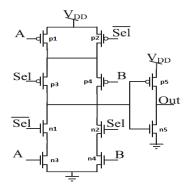

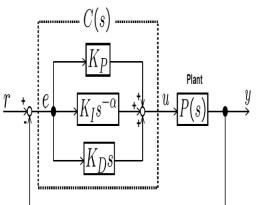

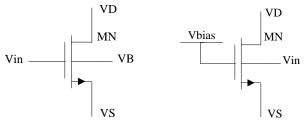

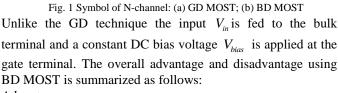

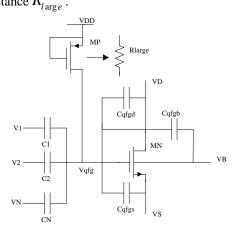

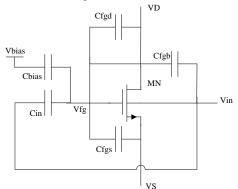

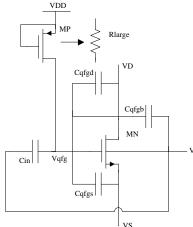

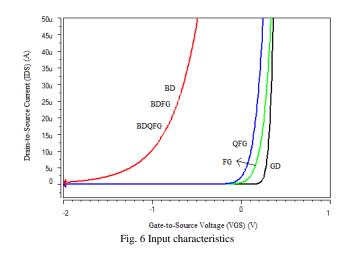

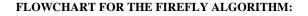

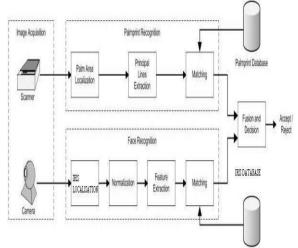

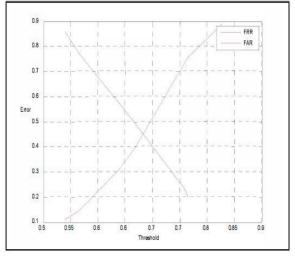

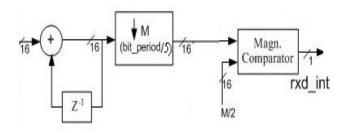

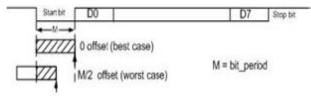

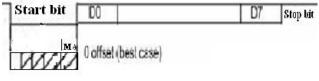

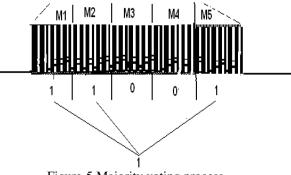

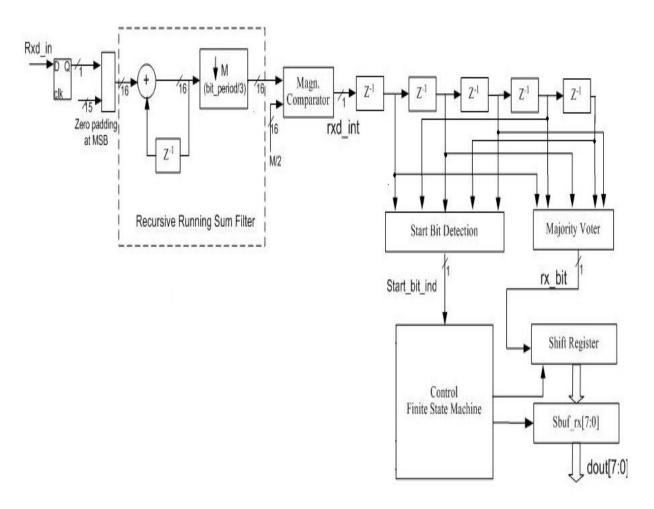

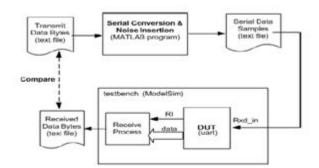

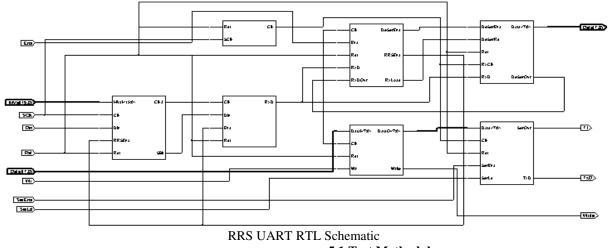

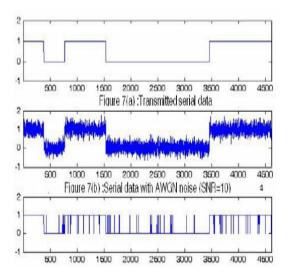

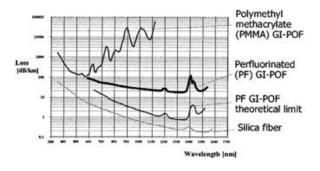

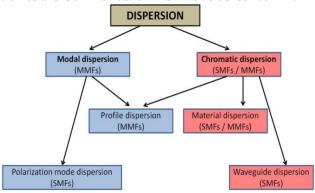

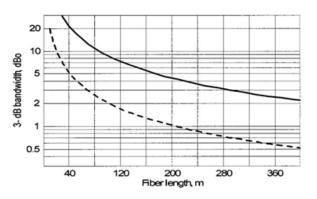

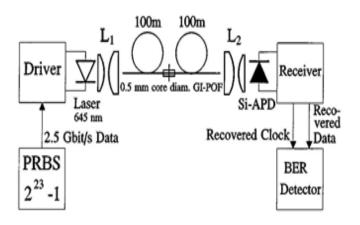

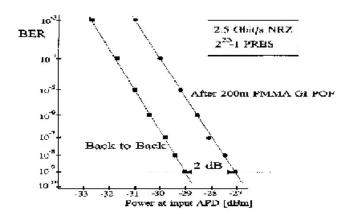

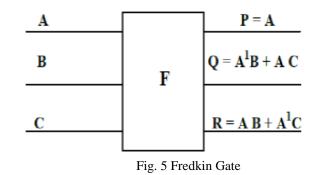

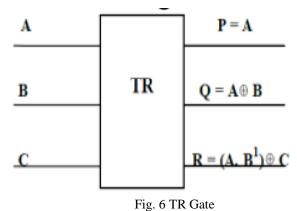

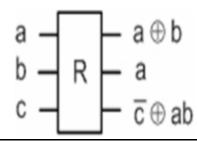

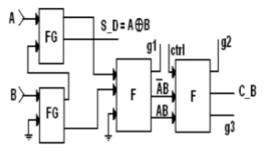

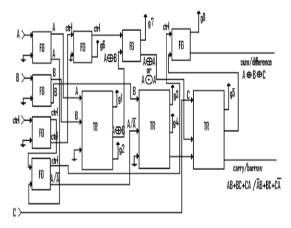

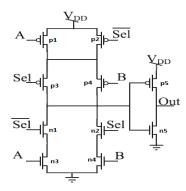

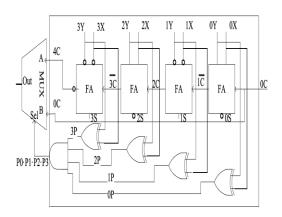

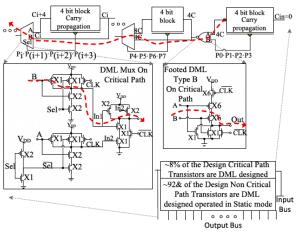

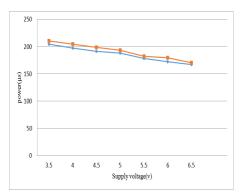

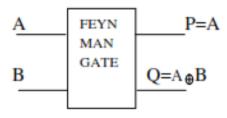

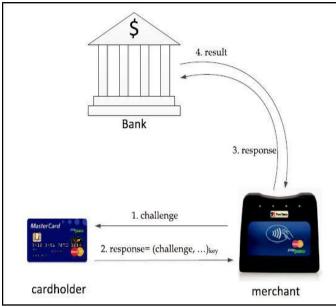

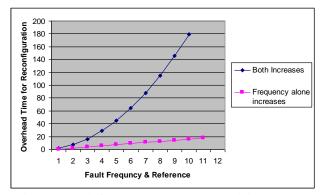

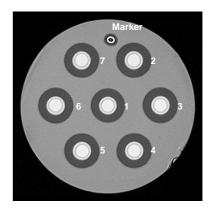

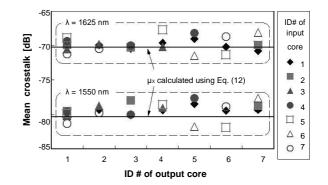

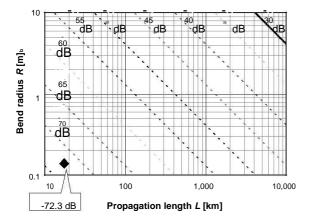

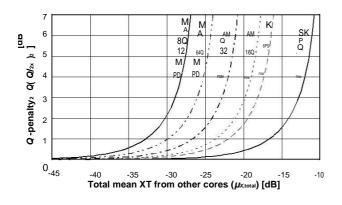

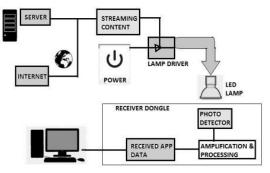

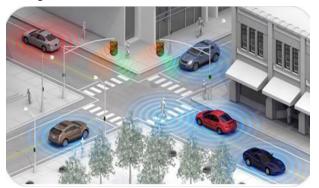

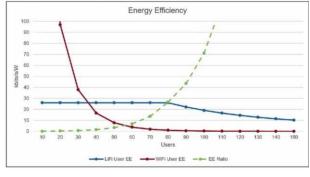

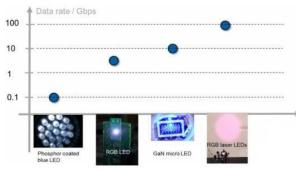

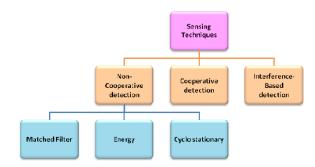

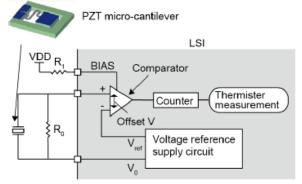

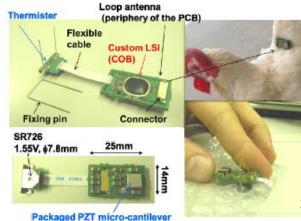

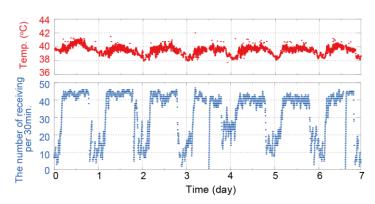

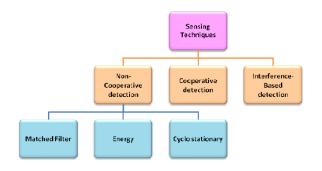

<sup>2</sup>spdhivyaa@gmail.com