# CONTEMPORARY LOGIC DESIGN

SECOND EDITION

RANDY H. KATZ · GAETANO BORRIELLO

# **Contemporary Logic Design**

**Second Edition**

Randy H. Katz University of California, Berkeley

Gaetano Borriello University of Washington

#### Library of Congress Cataloging-in-Publication Data

Katz, Randy H.,

Contemporary logic design / Randy H. Katz—2nd ed.

p. cm.

ISBN 02-0130857-6

1. Electronic digital computers—Circuits—Design. 2. Integrated circuits—Very large scale integration—Design—Data processing. 3. Logic design—Data processing. 4. Computer-aided design. I. Title.

TK7888.4.K36 2005 621.39'5—dc22

2004063209

Vice President and Editorial Director, ECS: Marcia J. Horton

Vice President and Director of Production and Manufacturing, ESM: David W. Riccardi

Executive Managing Editor: Vince O'Brien

Managing Editor: *David A. George* Production Editor: *Rose Kernan*

Director of Creative Services: Paul Belfanti

Art Director: Jayne Conte

Managing Editor, AV Management and Production: Patricia Burns

Art Editor: Xiaohong Zhu

Manufacturing Buyer: *Lisa McDowell* Senior Marketing Manager: *Holly Stark*

About the Cover: Image by Rene Magritte "Golconde" 1953. Menil Collection, Houston, TX, U.S.A./Giraudon/Art Resource, NY. © 2004 C. Herscovici, Brussels/Artists Rights Society (ARS), New York.

© 2005 Pearson Education, Inc.

Pearson Prentice Hall Pearson Education, Inc.

Upper Saddle River, New Jersey 07458

All rights reserved. No part of this book may be reproduced, in any form or by any means, without permission in writing from the publisher.

Pearson Prentice Hall<sup>TM</sup> is a trademark of Pearson Education, Inc.

The author and publisher of this book have used their best efforts in preparing this book. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this book. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of these programs.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

#### ISBN 0-201-30857-6

Pearson Education Ltd., London

Pearson Education Australia Pty, Ltd., Sydney

Pearson Education Singapore, Pte. Ltd.

Pearson Education North Asia Ltd., Hong Kong

Pearson Education Canada, Inc., Toronto

Pearson Educación de Mexico, S.A. de C.V.

Pearson Education—Japan, Tokyo

Pearson Education Malaysia, Pte. Ltd.

Pearson Education, Inc., Upper Saddle River, New Jersey

Dedicated to our students, who motivate, challenge, and make us proud every day.

# **Contents**

### Preface xiii

| Chapter 1 | Introduction 1                                    |  |  |  |  |

|-----------|---------------------------------------------------|--|--|--|--|

|           | 1.1 Dissecting the Title 2                        |  |  |  |  |

|           | 1.1.1 Design 2                                    |  |  |  |  |

|           | 1.1.2 Logic Design 4                              |  |  |  |  |

|           | 1.1.3 Contemporary Logic Design 6                 |  |  |  |  |

|           | 1.2 A Brief History of Logic Design 8             |  |  |  |  |

|           | 1.3 Computation 9                                 |  |  |  |  |

|           | 1.3.1 Switches, Relays, and Circuits 10           |  |  |  |  |

|           | 1.3.2 Transistors 12                              |  |  |  |  |

|           | 1.3.3 Digital Representations 13                  |  |  |  |  |

|           | 1.3.4 Encoding 14 <b>1.4 Examples 15</b>          |  |  |  |  |

|           |                                                   |  |  |  |  |

|           | Chapter Review 25                                 |  |  |  |  |

|           | Further Reading 27                                |  |  |  |  |

|           | Exercises 28                                      |  |  |  |  |

| Chapter 2 | Combinational Logic 33                            |  |  |  |  |

|           | 2.1 Outputs as a Function of Inputs 34            |  |  |  |  |

|           | 2.1.1 Combinational Logic Defined 34              |  |  |  |  |

|           | 2.1.2 Examples of Combinational Logic 34          |  |  |  |  |

|           | 2.2 Laws and Theorems of Boolean Logic 37         |  |  |  |  |

|           | 2.2.1 Axioms of Boolean Algebra 39                |  |  |  |  |

|           | 2.2.2 Theorems of Boolean Algebra 42              |  |  |  |  |

|           | 2.2.3 Duality and DeMorgan's Law 45               |  |  |  |  |

|           | 2.3 Realizing Boolean Formulas 46                 |  |  |  |  |

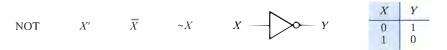

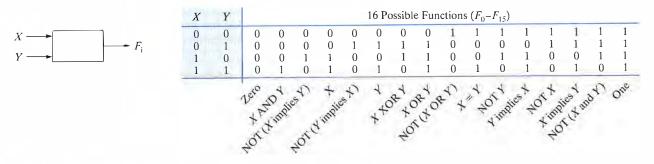

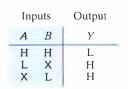

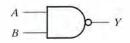

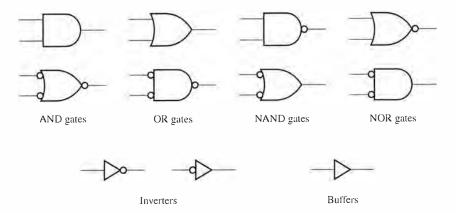

|           | 2.3.1 Logic Gates 46                              |  |  |  |  |

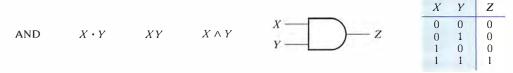

|           | 2.3.2 Logic Blocks and Hierarchy 49               |  |  |  |  |

|           | 2.3.3 Time Behavior and Waveforms 50              |  |  |  |  |

|           | 2.3.4 Minimizing the Number of Gates and Wires 52 |  |  |  |  |

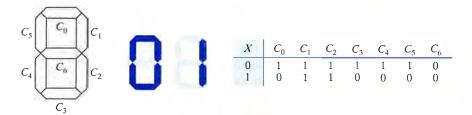

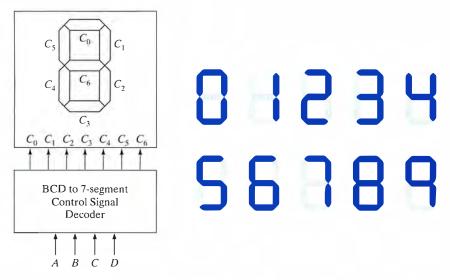

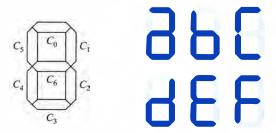

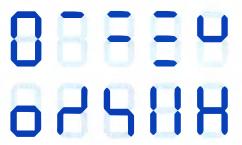

|           | 2 3 5 Case Study: 7-Segment Decoder 54            |  |  |  |  |

| 2.4 Two-Level Logic 56                                              |

|---------------------------------------------------------------------|

| 2.4.1 Canonical Forms 56                                            |

| 2.4.2 Incompletely Specified Functions 63                           |

| 2.5 Motivation for Two-Level Simplification 65                      |

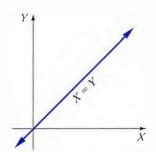

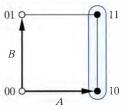

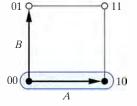

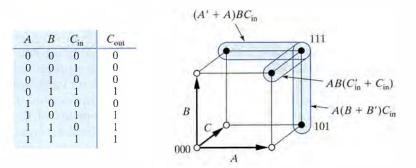

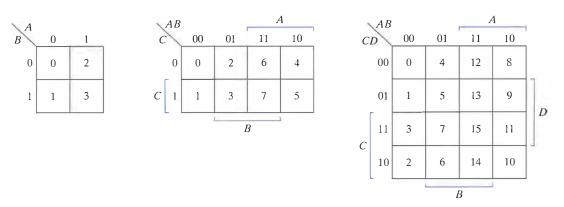

| 2.5.1 Graphing Boolean Expressions 66                               |

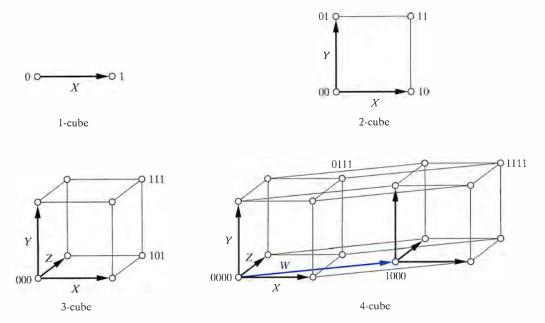

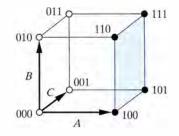

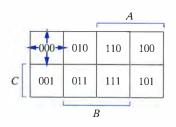

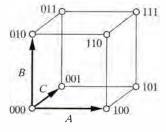

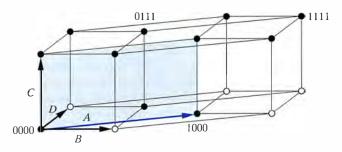

| 2.5.2 Boolean Cubes 67                                              |

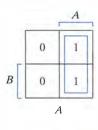

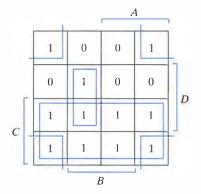

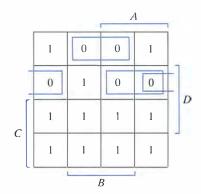

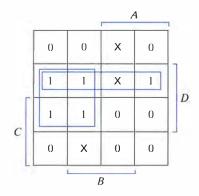

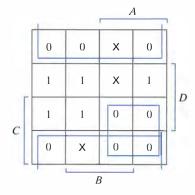

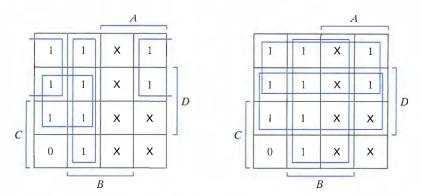

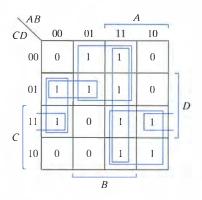

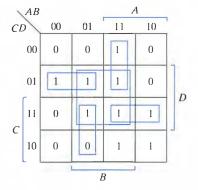

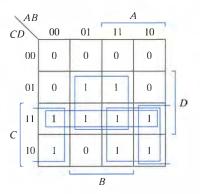

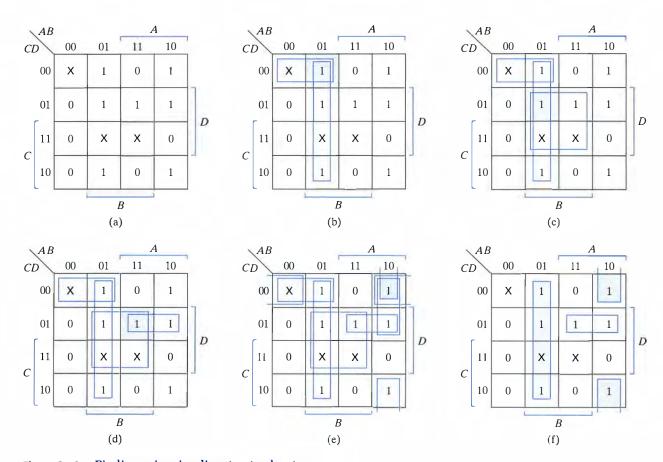

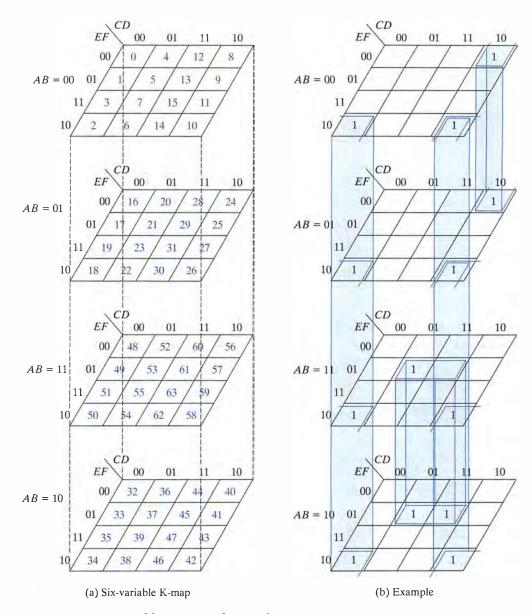

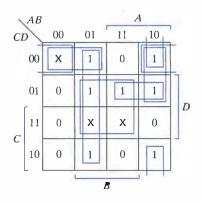

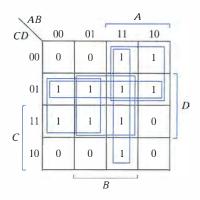

| 2.5.3 Karnaugh Maps 69                                              |

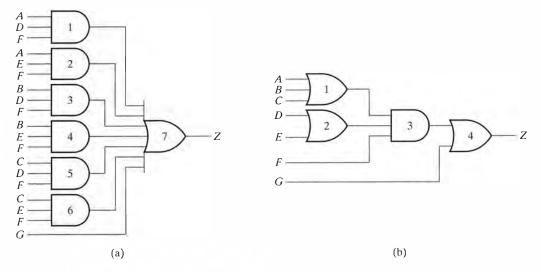

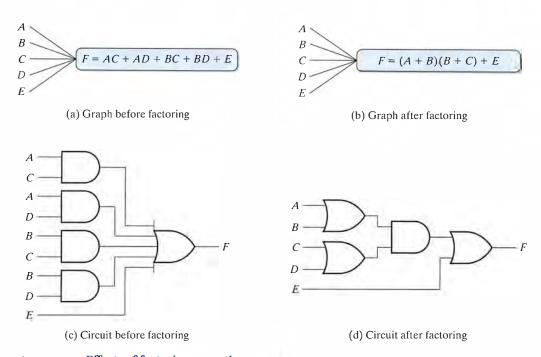

| 2.6 Multilevel Logic 76                                             |

| 2.7 Motivation for Multilevel Minimization 80                       |

| 2.7.1 Factored Forms 80                                             |

| 2.7.2 Criteria for Multilevel Simplification 81                     |

| Chapter Review 83                                                   |

| Further Reading 84                                                  |

| Exercises 85                                                        |

|                                                                     |

| Working with Combinational Logic 93                                 |

| 3.1 Two-Level Simplification 93                                     |

| 3.1.1 Formalizing the Process of Boolean                            |

| Minimization 99                                                     |

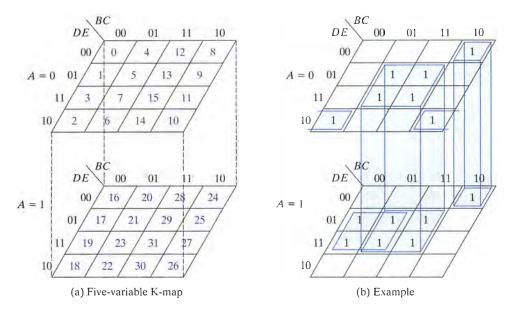

| 3.1.2 K-Maps Revisited: Five- and Six-Variable                      |

| Functions 102                                                       |

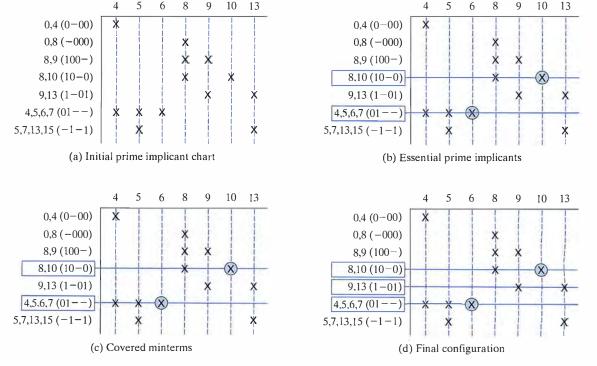

| 3.2 Automating Two-Level Simplification 103                         |

| 3.2.1 Quine-McCluskey Method 104                                    |

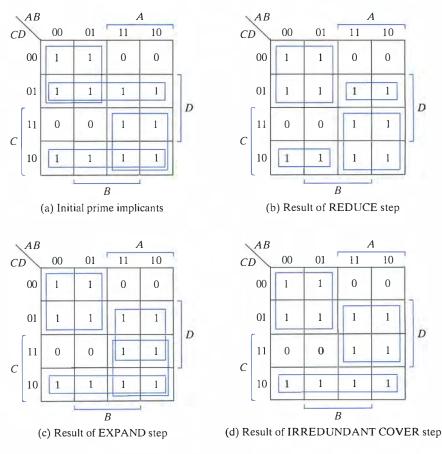

| 3.2.2 Espresso Method 108                                           |

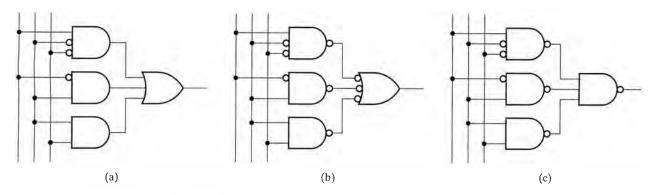

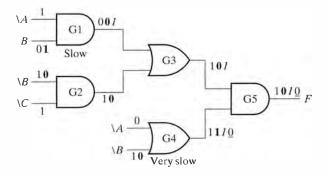

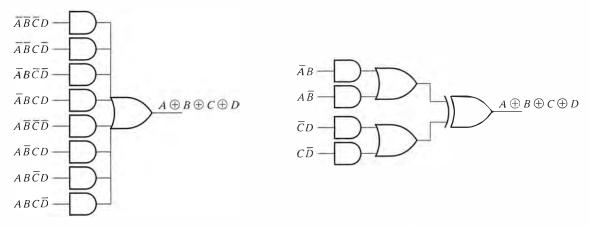

| 3.2.3 Realizing S-o-P and P-o-S Logic Networks 111                  |

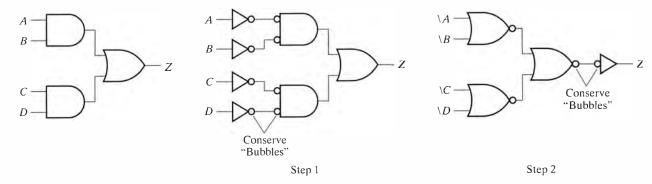

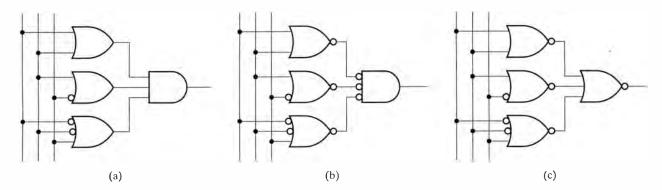

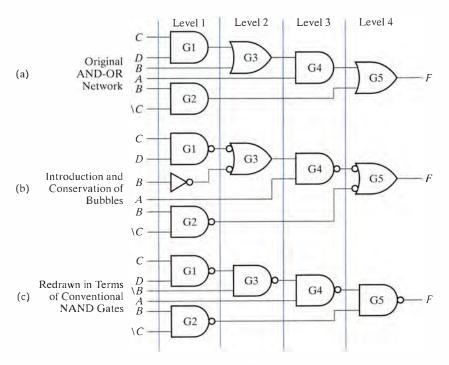

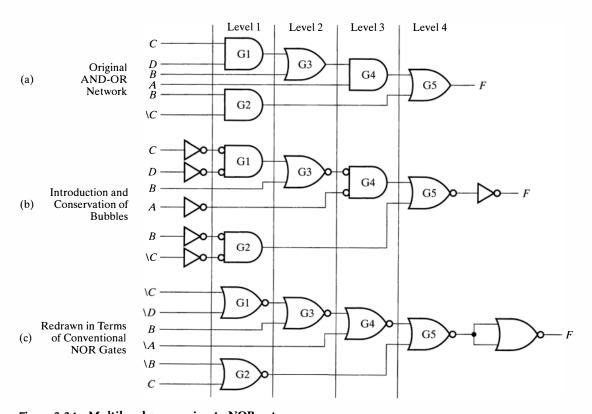

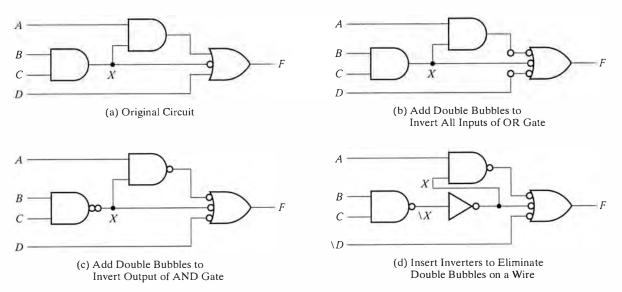

| 3.3 Multilevel Simplification 114                                   |

| 3.4 Automating Multilevel Simplification 122                        |

| 3.4.1 Multilevel Logic Optimization Scripts 122                     |

| 3.4.2 Realizing Multilevel Logic Networks 126                       |

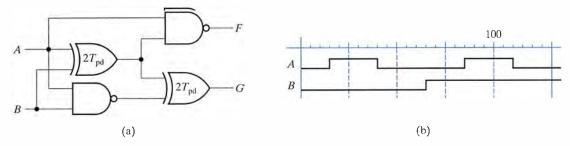

| 3.5 Time Response in Combinational                                  |

| Networks 129                                                        |

| 3.5.1 Gate Delays 129                                               |

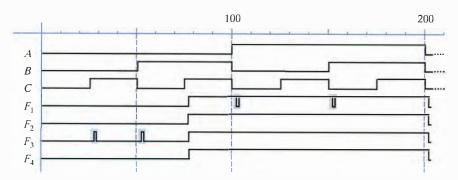

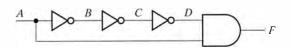

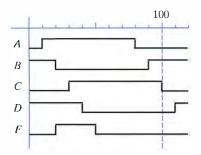

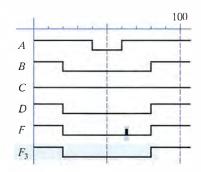

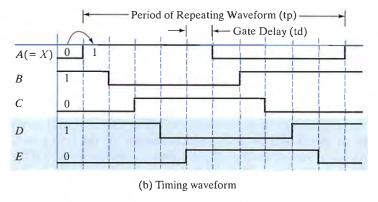

| 3.5.2 Timing Waveforms 130                                          |

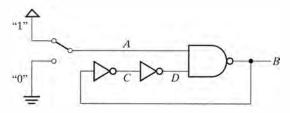

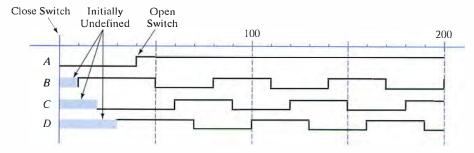

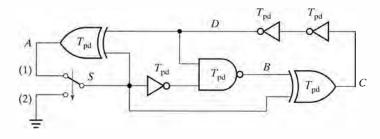

| 3.5.3 Analysis of a Pulse-Shaper Circuit 131                        |

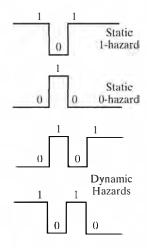

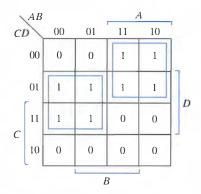

| 3.5.4 Hazards and Glitches 132                                      |

| 3.5.5 Hazard Detection and Elimination in<br>Two-Level Networks 133 |

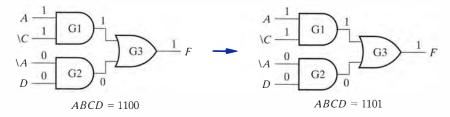

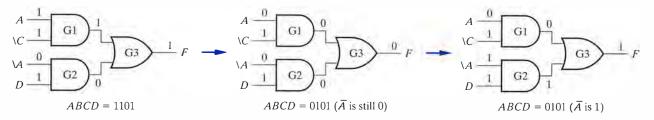

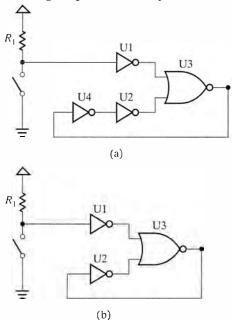

| 3.5.6 Static Hazards in Multilevel Networks 136                     |

| 3.5.7 Designing Static Hazard-Free Multilevel Circuits 137          |

| 3.5.8 Dynamic Hazards 138                                           |

|                                                                     |

| 3.6 Hardware Description Languages 139     |     |

|--------------------------------------------|-----|

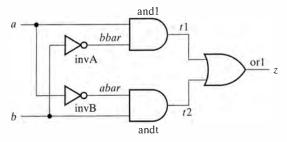

| 3.6.1 Describing Structure 141             |     |

| 3.6.2 Describing Behavior 141              |     |

| 3.6.3 Delay 143                            |     |

| 3.6.4 Event-Driven Simulation 143          |     |

| Chapter Review 146                         |     |

| Further Reading 146                        |     |

| Exercises 147                              |     |

|                                            |     |

| Combinational Logic                        |     |

| Technologies 155                           |     |

| 3                                          |     |

| 4.1 History 156                            |     |

| 4.1.1 From Switches to Integrated Circuits | 156 |

| 4.1.2 Packaged Logic, Configurability, and |     |

| Programmable Logic 158                     |     |

4.1.3 Technology Metrics 162

#### 4.2 Basic Logic Components 164

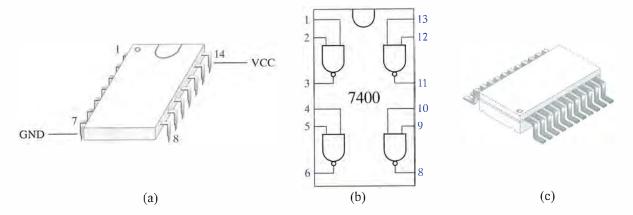

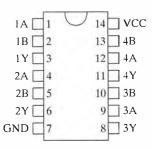

- 4.2.1 Fixed Logic 164

- 4.2.2 Look-Up Tables 168

- 4.2.3 Template-Based Logic 179

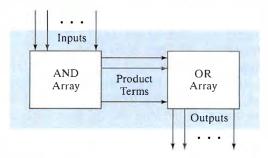

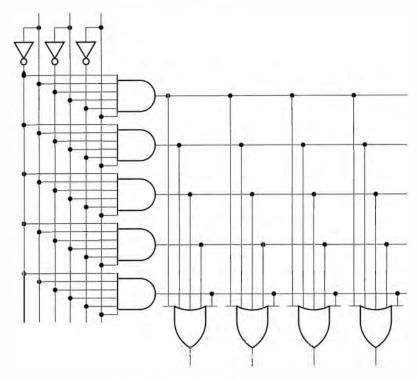

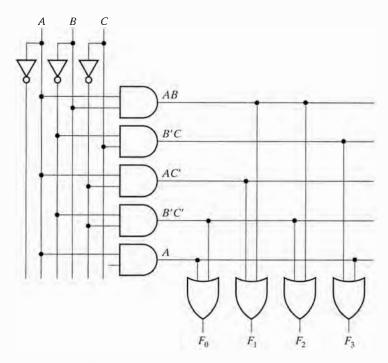

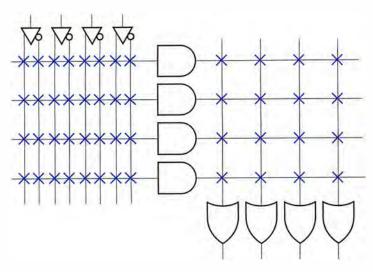

#### 4.3 Two-Level and Multilevel Logic 196

#### 4.4 Non-Gate Logic 205

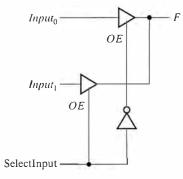

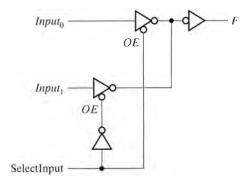

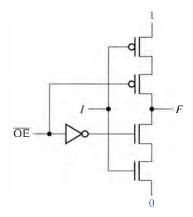

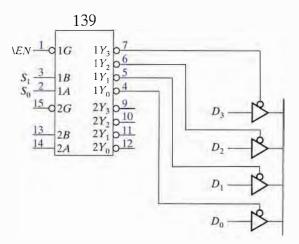

- 4.4.1 Tri-State Outputs 206

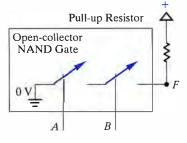

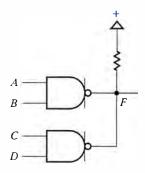

- 4.4.2 Open-Collector Outputs and Wired Logic 210

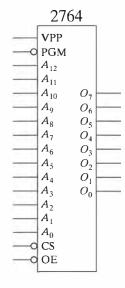

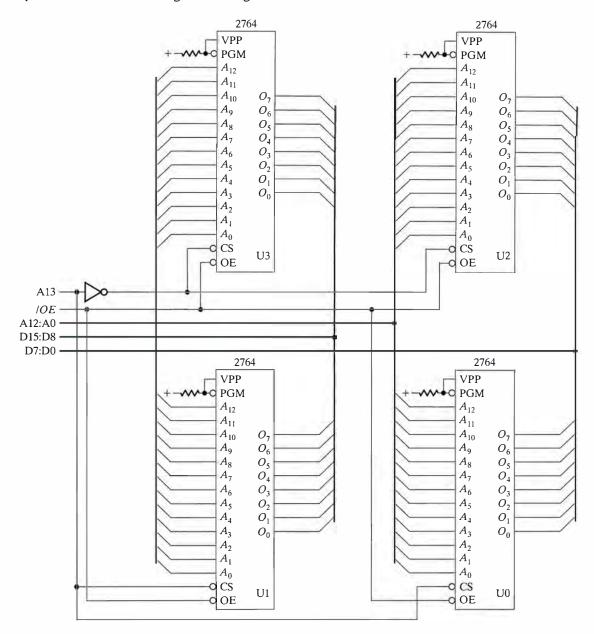

Chapter Review 212 Further Reading 213 Exercises 213

#### Chapter 5 Case Studies in Combinational Logic Design 221

- 5.1 Design Procedure 222

- 5.2 A Simple Process Line-Control Problem 224

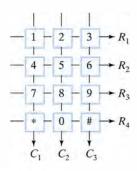

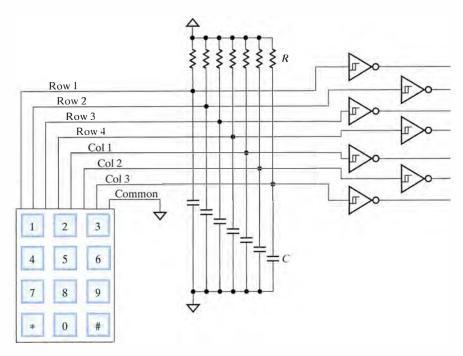

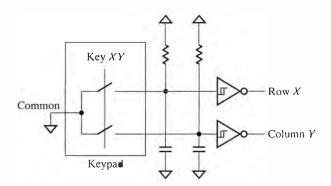

- 5.3 Telephone Keypad Decoder 227

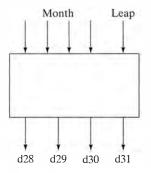

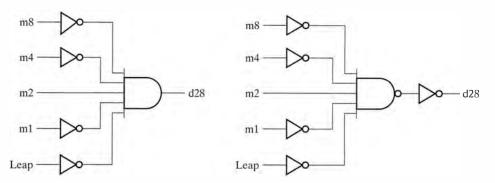

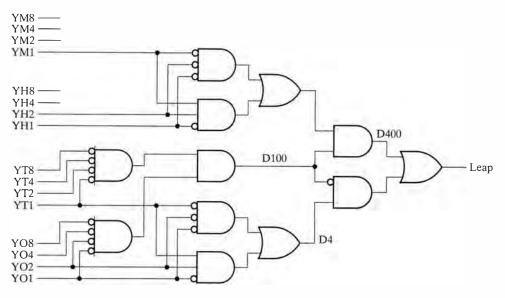

- 5.4 Leap Year Calculation 231

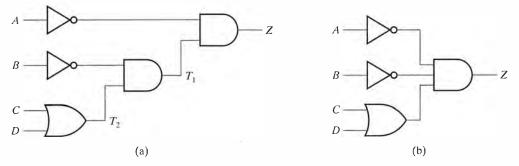

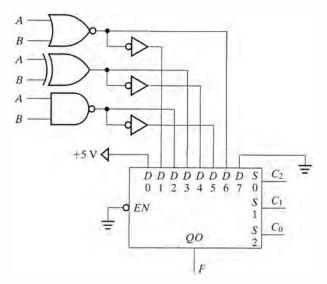

- 5.5 Logic Function Unit 234

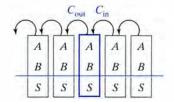

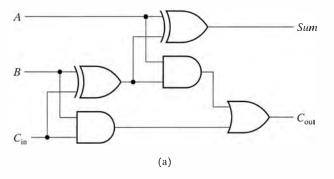

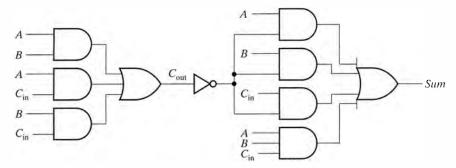

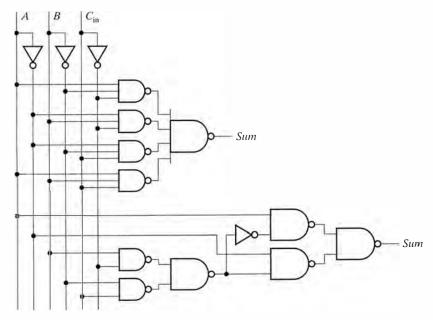

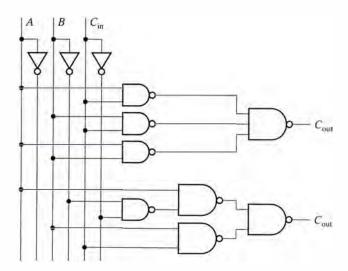

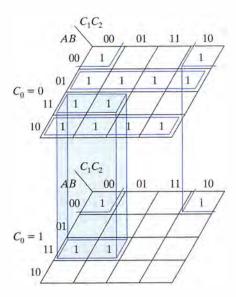

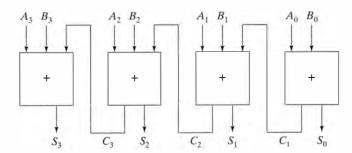

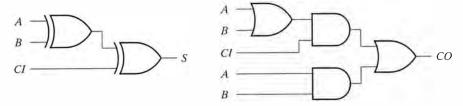

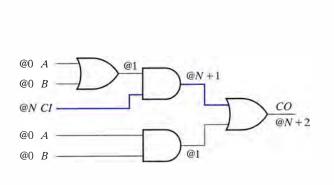

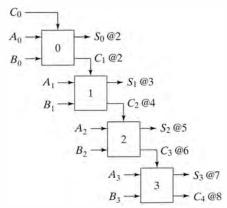

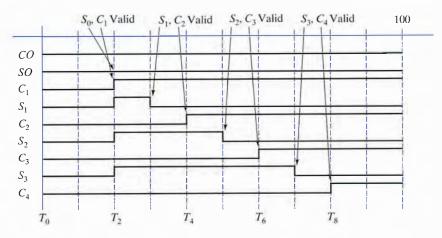

- 5.6 Adder Design 238

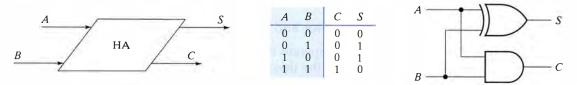

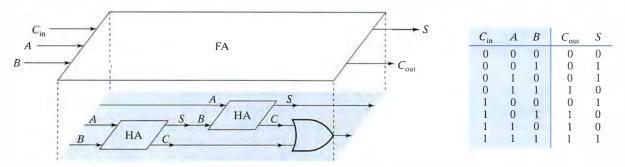

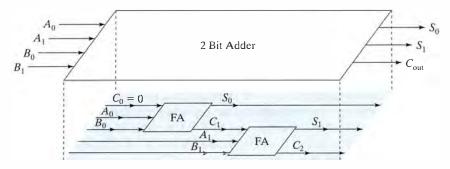

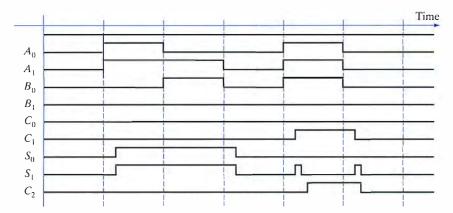

- 5.6.1 Half Adder/Full Adder 238

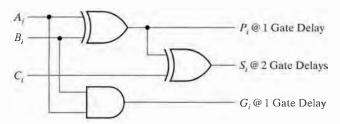

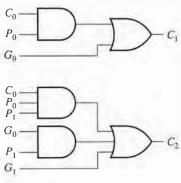

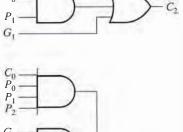

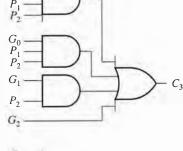

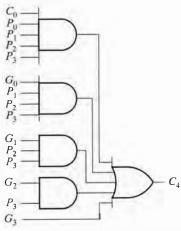

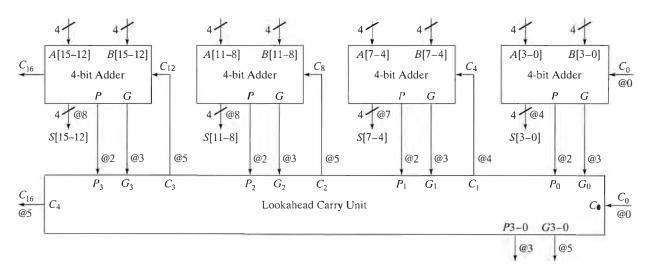

- 5.6.2 Carry-Lookahead Circuits 240

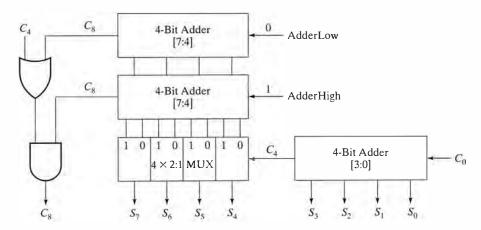

- 5.6.3 Carry-Select Adder 244

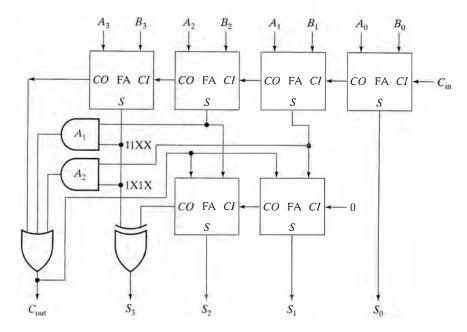

- 5.6.4 BCD Adder Design 245

Chapter 7

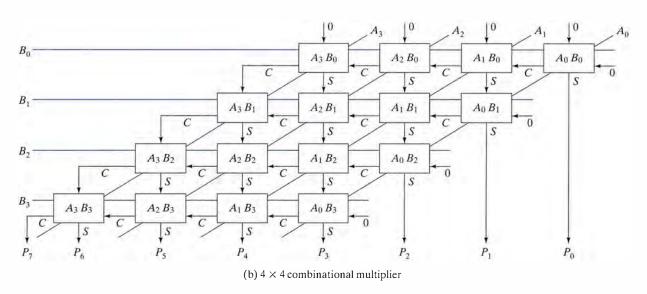

| <ul> <li>5.7 Arithmetic Logic Unit Design 246 <ul> <li>5.7.1 A Sample ALU 247</li> </ul> </li> <li>5.8 Combinational Multiplier 249</li> <li>Chapter Review 253</li> <li>Further Reading 253</li> <li>Exercises 254</li> </ul>                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sequential Logic Design 259                                                                                                                                                                                                                                                                                        |

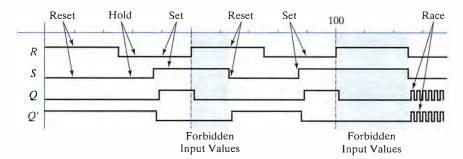

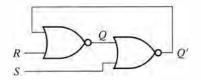

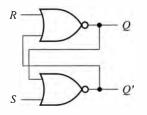

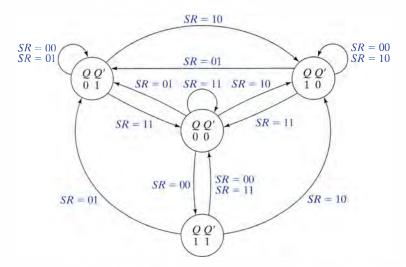

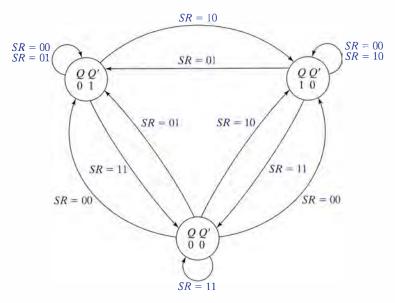

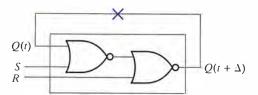

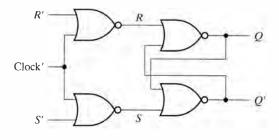

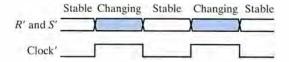

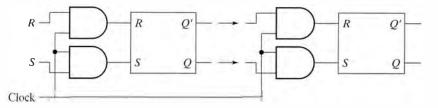

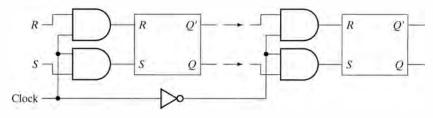

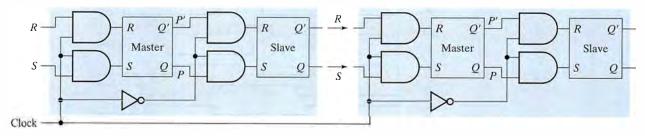

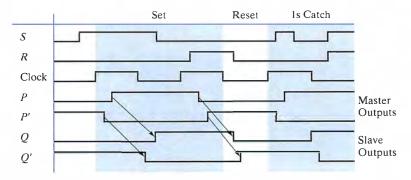

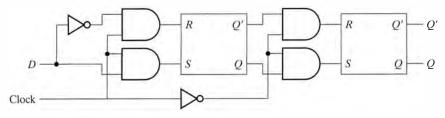

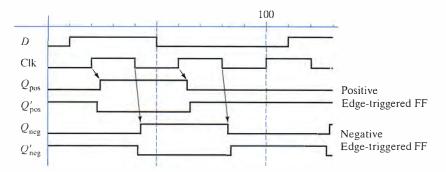

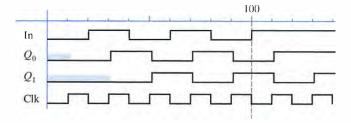

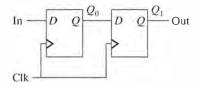

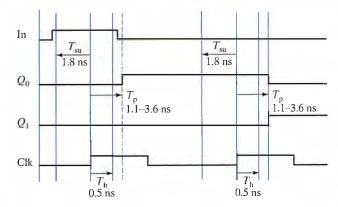

| <ul> <li>6.1 Sequential Logic Elements 260</li> <li>6.1.1 Simple Circuits with Feedback 260</li> <li>6.1.2 Basic Latches 265</li> <li>6.1.3 Clocks 267</li> <li>6.1.4 Combining Latches 268</li> <li>6.1.5 Master–Slave Latches and Edge-Triggered Flip-Flops 270</li> <li>6.1.6 Timing Definitions 273</li> </ul> |

| 6.2 Timing Methodologies 278                                                                                                                                                                                                                                                                                       |

| 6.2.1 Cascaded Flip-Flops and Setup/Hold/<br>Propagation 279                                                                                                                                                                                                                                                       |

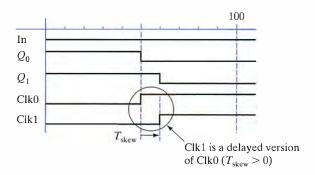

| 6.2.2 Clock Skew 281                                                                                                                                                                                                                                                                                               |

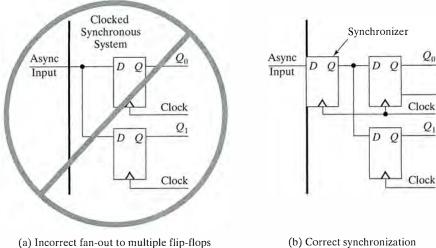

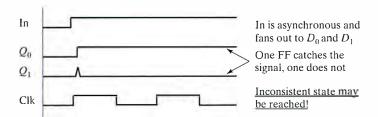

| 6.2.3 Asynchronous Inputs 282                                                                                                                                                                                                                                                                                      |

| 6.2.4 Metastability and Synchronizer Failure 284                                                                                                                                                                                                                                                                   |

| 6.2.5 Self-timed and Speed-independent<br>Circuits 285                                                                                                                                                                                                                                                             |

| 6.3 Registers 289                                                                                                                                                                                                                                                                                                  |

| 6.3.1 Storage Registers 289                                                                                                                                                                                                                                                                                        |

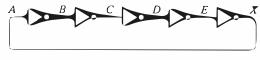

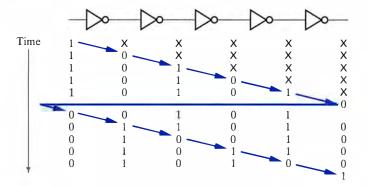

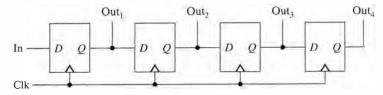

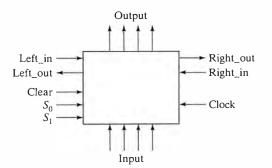

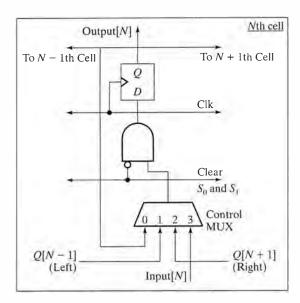

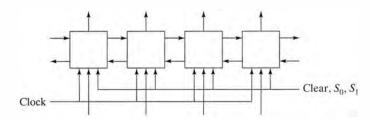

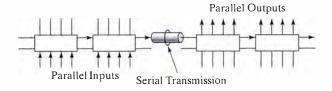

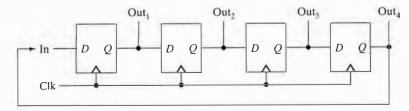

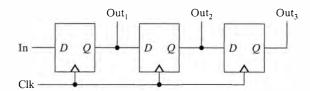

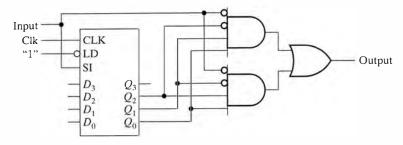

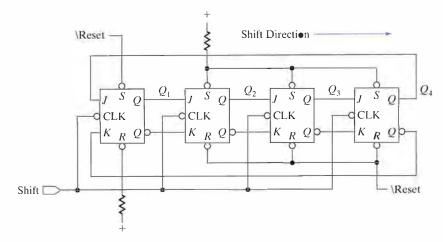

| 6.3.2 Shift Registers 291                                                                                                                                                                                                                                                                                          |

| 6.4 Hardware Description Languages 295                                                                                                                                                                                                                                                                             |

| Chapter Review 298                                                                                                                                                                                                                                                                                                 |

| Further Reading 299                                                                                                                                                                                                                                                                                                |

| Exercises 300                                                                                                                                                                                                                                                                                                      |

| Finite State Machines 307                                                                                                                                                                                                                                                                                          |

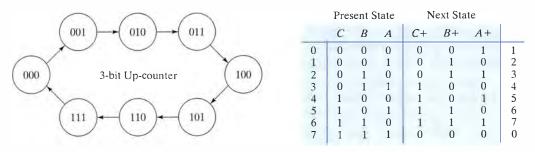

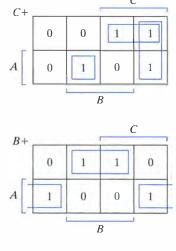

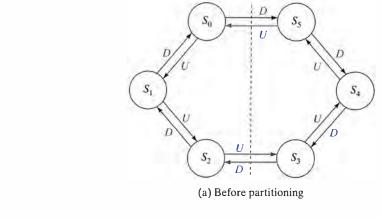

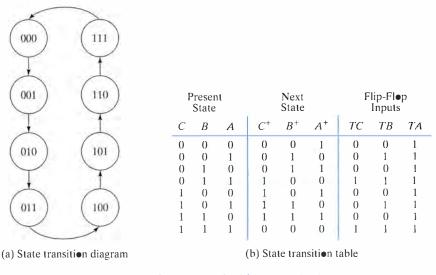

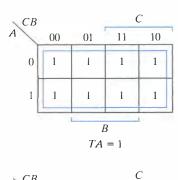

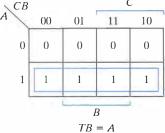

| 7.1 Counters 308                                                                                                                                                                                                                                                                                                   |

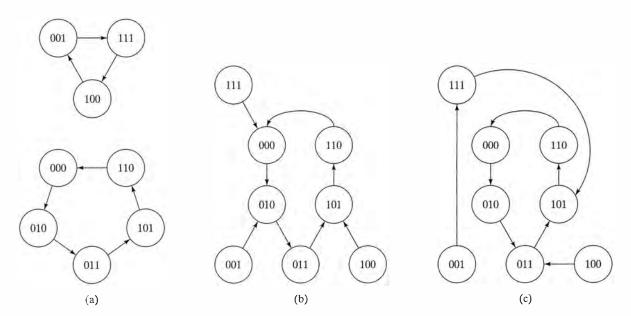

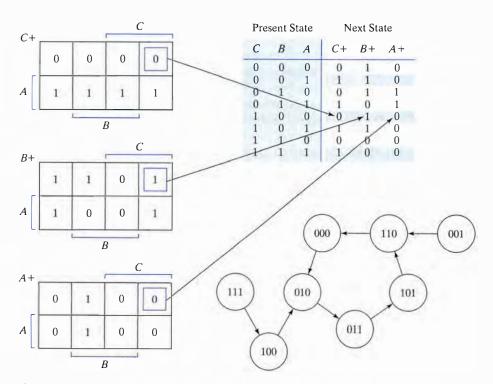

| 7.1.1 Counter Design Procedure 310                                                                                                                                                                                                                                                                                 |

| 7.1.2 Counters with More Complex Sequencing 312                                                                                                                                                                                                                                                                    |

| 7.1.3 Self-Starting Counters 314                                                                                                                                                                                                                                                                                   |

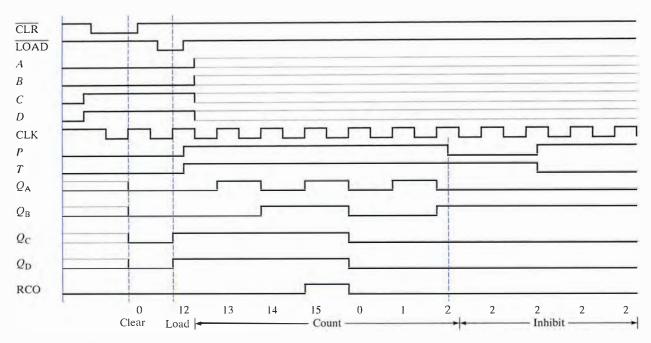

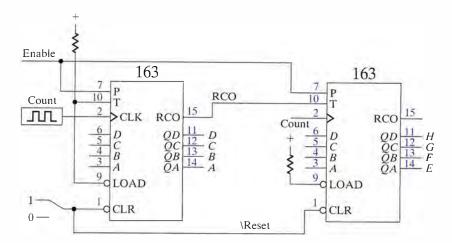

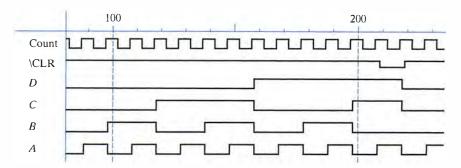

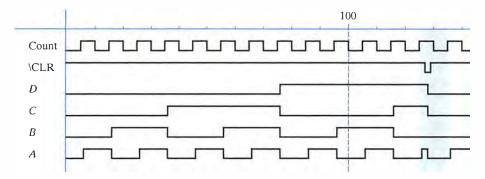

| 7.1.4 Counter Reset 316                                                                                                                                                                                                                                                                                            |

| 7.1.5. Countar Variations 216                                                                                                                                                                                                                                                                                      |

| 7.2 | The C            | oncept of the State Machine 321         |

|-----|------------------|-----------------------------------------|

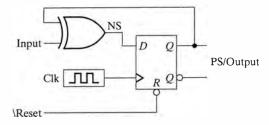

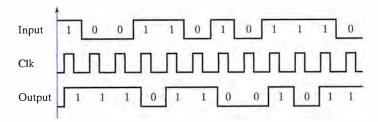

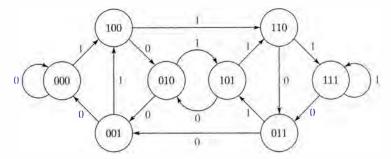

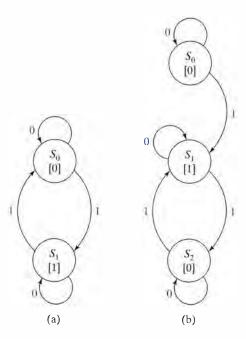

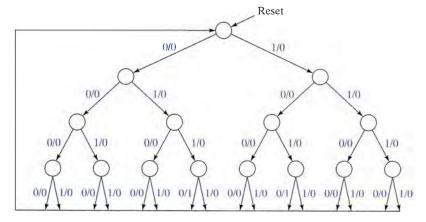

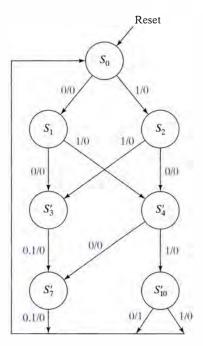

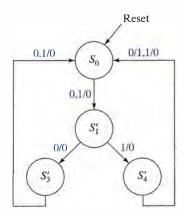

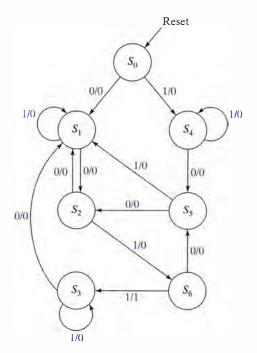

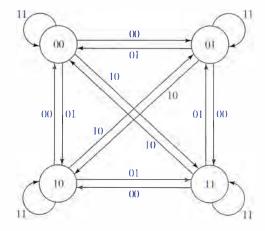

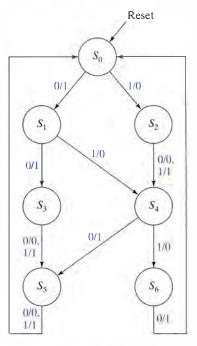

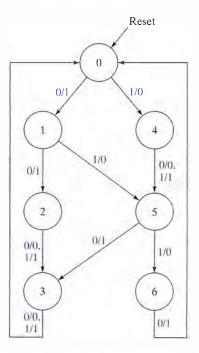

|     |                  | Odd or Even Parity Checker 321          |

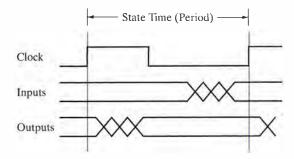

|     | 7.2.2            | Timing in State Machines 324            |

| 7.3 | Basic            | FSM Design Approach 326                 |

|     | 7.3.1            | Finite State Machine Design             |

|     |                  | Procedure 327                           |

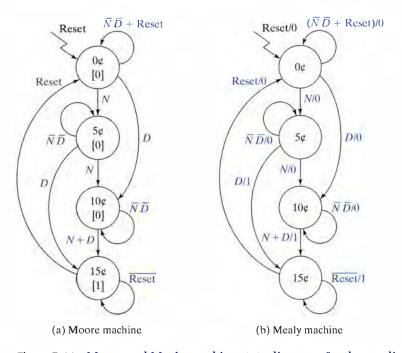

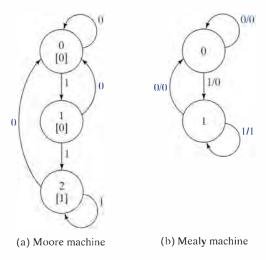

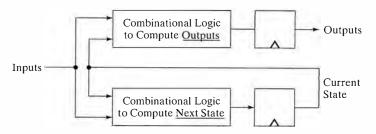

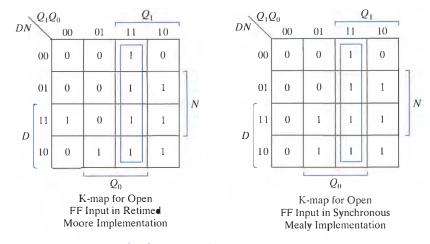

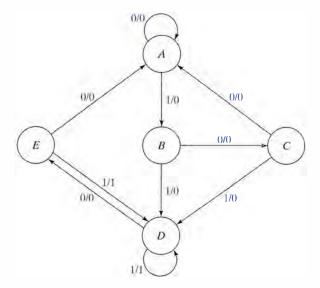

|     | 7.3.2            | Moore and Mealy Machines 332            |

|     |                  | State Diagram Representation 333        |

|     | 7.3.4            | Comparison of the Two Machine Types 334 |

| 7.4 | Motiv            | vation for Optimization 339             |

|     |                  | Two State Diagrams, Same I/O            |

|     |                  | Behavior 339                            |

|     |                  | Advantages of Minimum States 340        |

|     |                  | State, Input, and Output Encoding 341   |

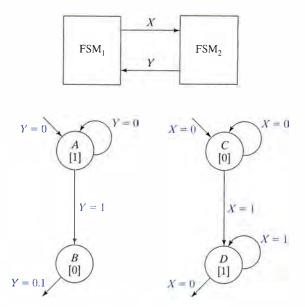

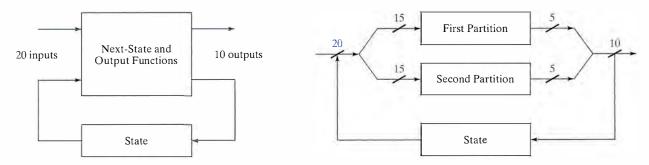

|     |                  | Factoring State Machines 342            |

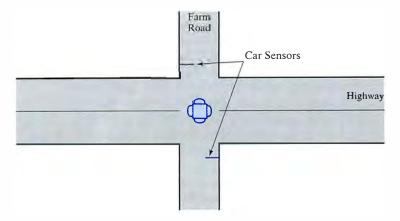

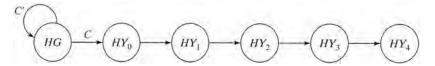

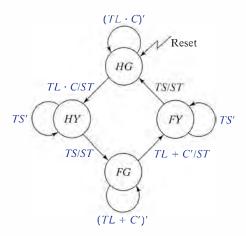

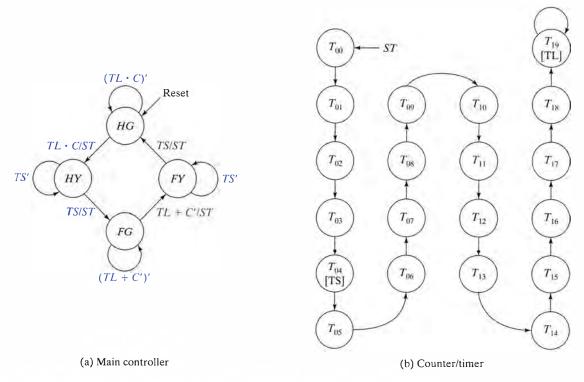

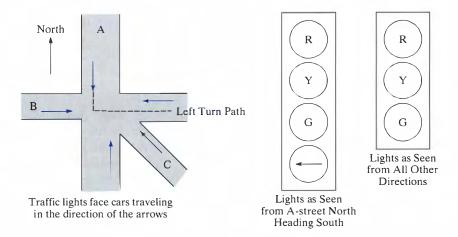

|     |                  | A Traffic-Light Controller 342          |

|     | -                | eview 346                               |

|     |                  | eading 347                              |

| Exe | rcises           | 348                                     |

|     |                  |                                         |

| Wo  | rking            | g with Finite State Machines 355        |

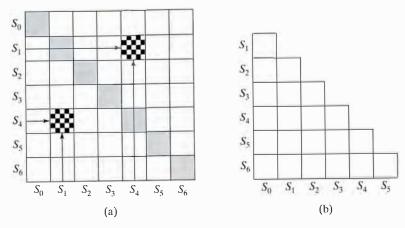

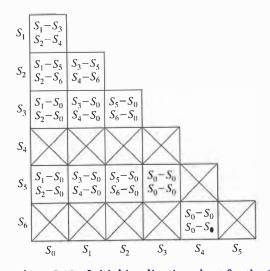

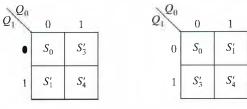

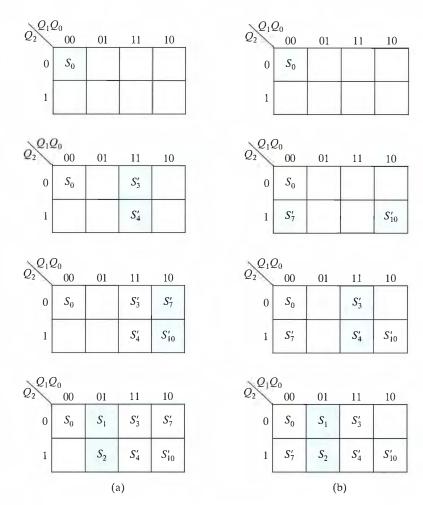

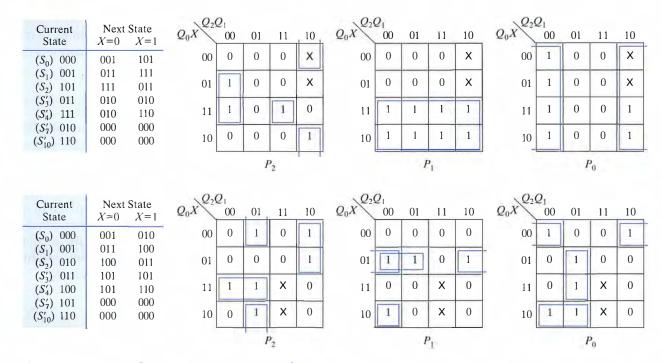

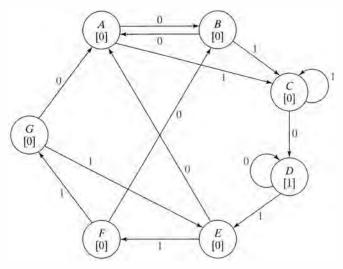

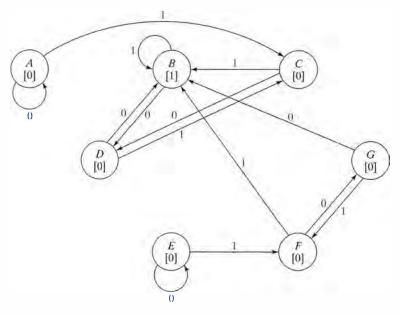

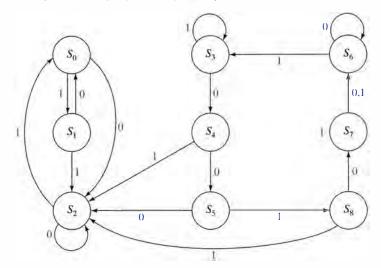

| 8.1 | State            | Minimization/Reduction 356              |

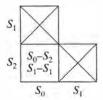

|     | 8.1.1            | Row-Matching Method 356                 |

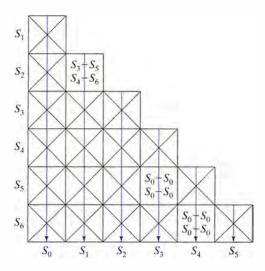

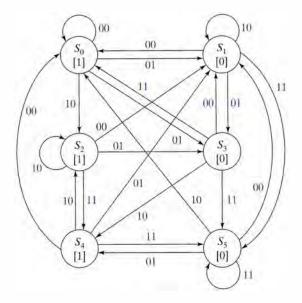

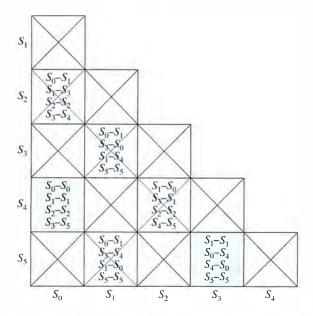

|     | 8.1.2            | Implication Chart Method 360            |

|     | 8.1.3            | Equivalent States in the Presence       |

|     |                  | of Don't Cares 365                      |

|     | 8.1.4            | When State Minimization                 |

|     |                  | Doesn't Help 366                        |

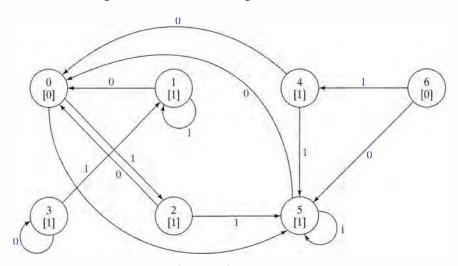

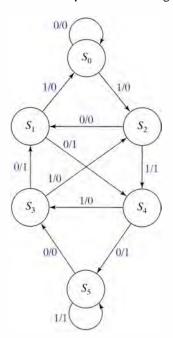

| 8.2 |                  | Assignment 367                          |

|     |                  | Sequential Encoding 369                 |

|     |                  | Random Encoding 370                     |

|     |                  | One-Hot Encoding 371                    |

|     |                  | Output-Oriented Encoding 372            |

|     |                  | Heuristic Methods 374                   |

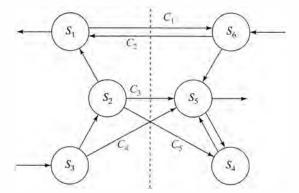

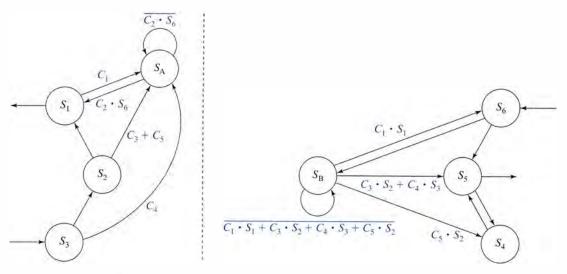

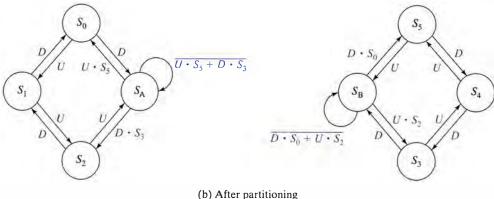

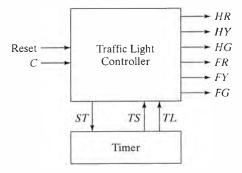

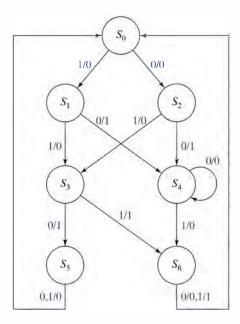

| 8.3 |                  | State Machine Partitioning 380          |

|     | 8.3.1            | Finite State Machine Partitioning by    |

| 0.4 | l la nale        | Introducing Idle States 381             |

|     |                  | vare Description Languages 386          |

|     | -                | eview 391<br>eading 392                 |

|     | ner Ke<br>rcises |                                         |

| LYG | いいっとう            | JJL                                     |

| Chapter 9  | Sequential Logic Technologies 401                                                                                                                                                                                                                                                                                                |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

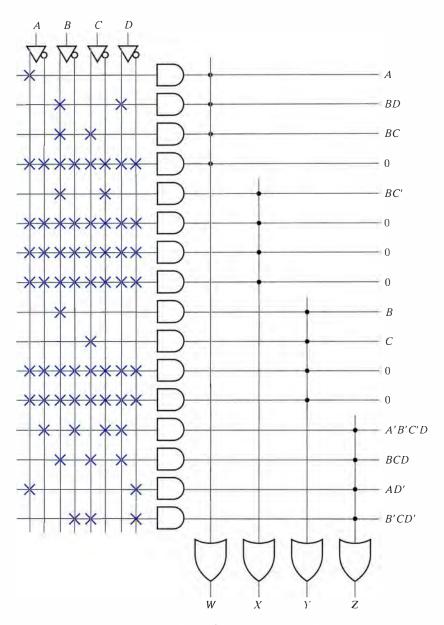

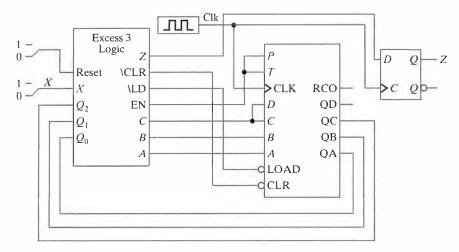

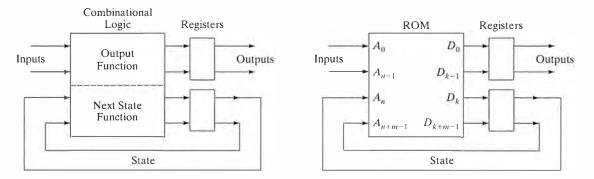

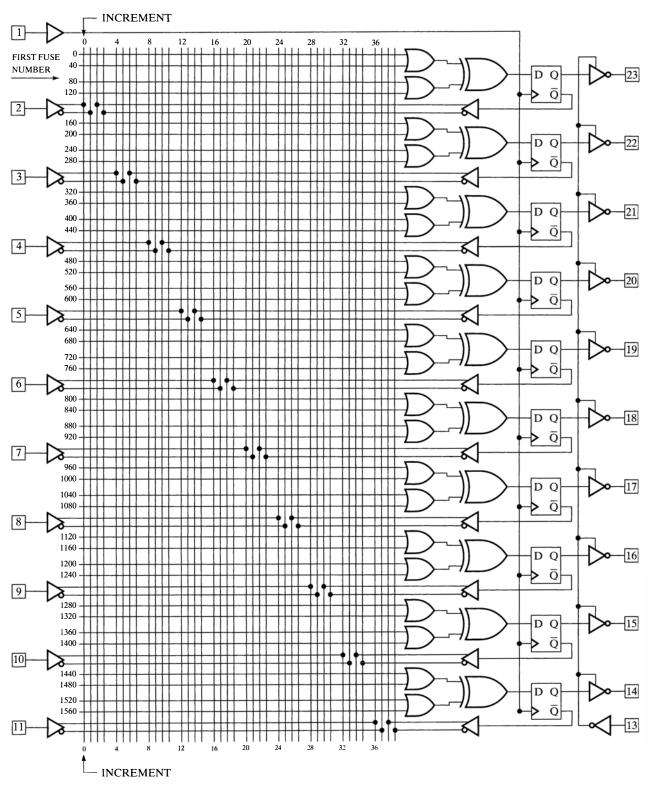

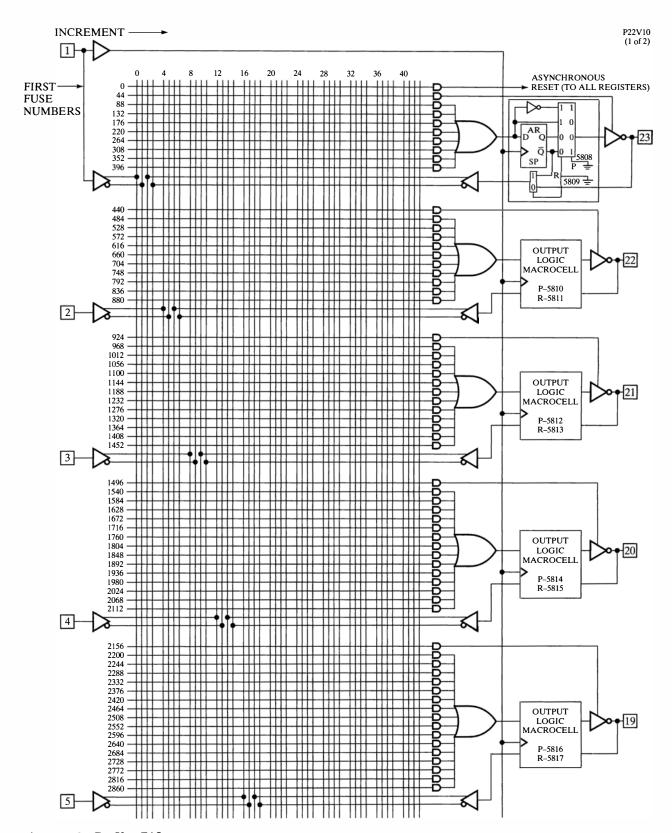

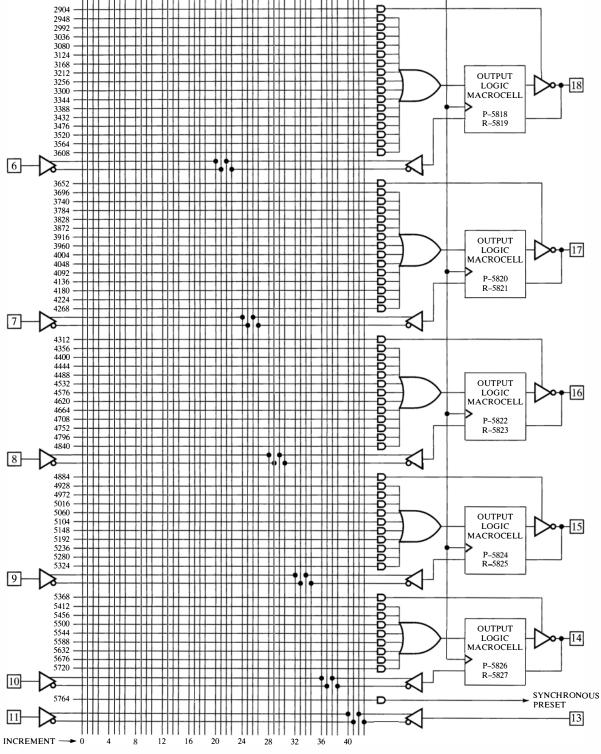

|            | <ul> <li>9.1 Basic Sequential Logic Components 402</li> <li>9.2 FSM Design with Counters 406</li> <li>9.3 FSM Design with Programmable Logic 409</li> <li>9.3.1 Mapping a State Machine into a ROM Implementation 409</li> <li>9.3.2 ROM Versus PLA-Based Design 410</li> <li>9.3.3 Alternative PAL Architectures 415</li> </ul> |  |  |  |

|            | 9.4 FSM Design with More Sophisticated Programmable Logic Devices 421                                                                                                                                                                                                                                                            |  |  |  |

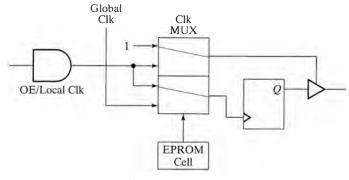

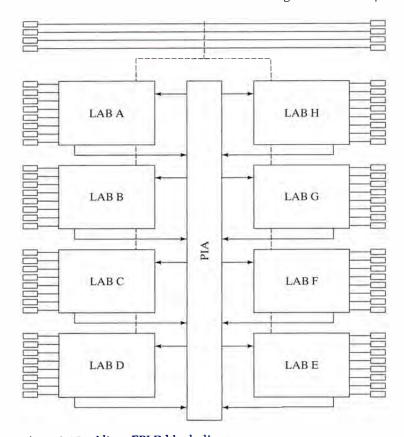

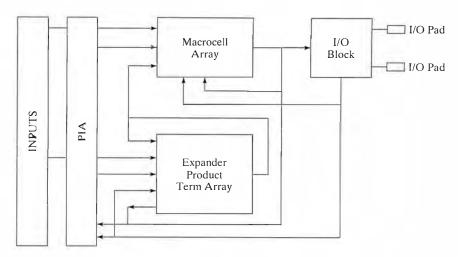

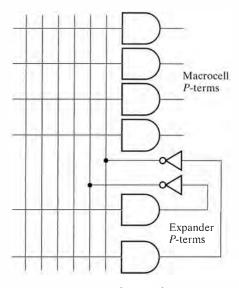

|            | 9.4.1 PLDs: Programmable Logic Devices 422                                                                                                                                                                                                                                                                                       |  |  |  |

|            | 9.4.2 Altera Erasable Programmable Logic Devices 422                                                                                                                                                                                                                                                                             |  |  |  |

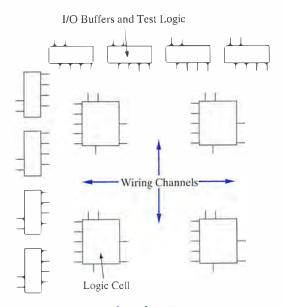

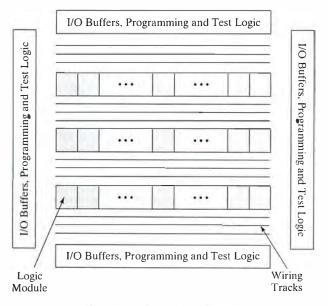

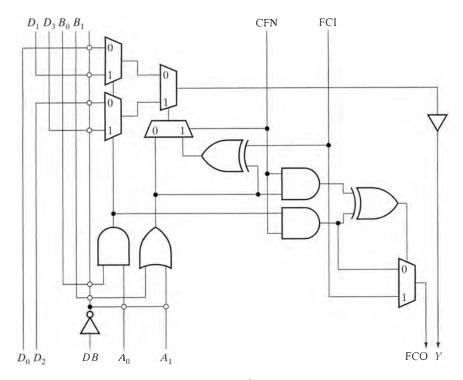

|            | 9.4.3 Actel Field-Programmable Gate Arrays 429                                                                                                                                                                                                                                                                                   |  |  |  |

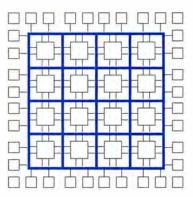

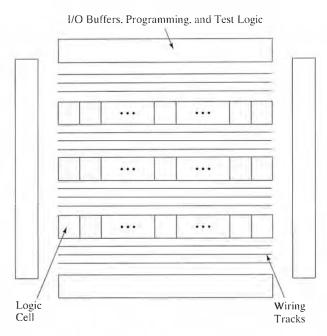

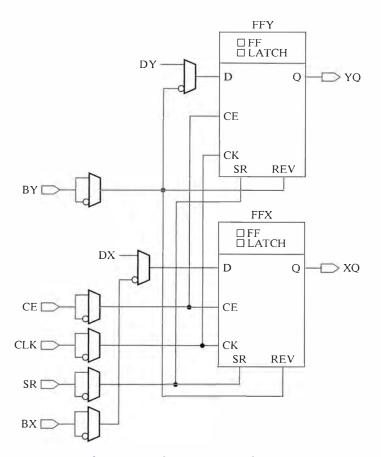

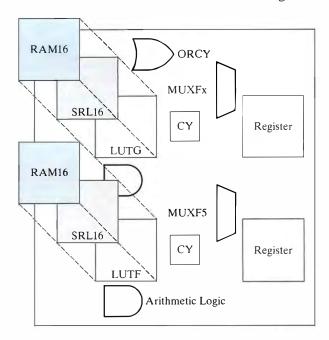

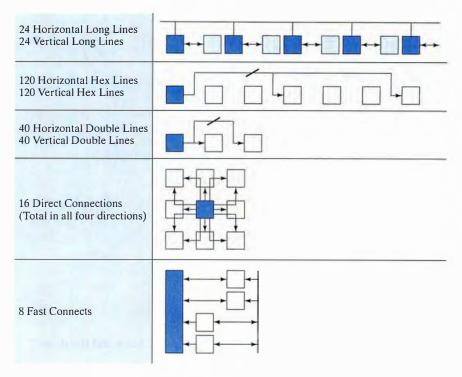

|            | 9.4.4 Xilinx Field Programmable Gate Arrays 432                                                                                                                                                                                                                                                                                  |  |  |  |

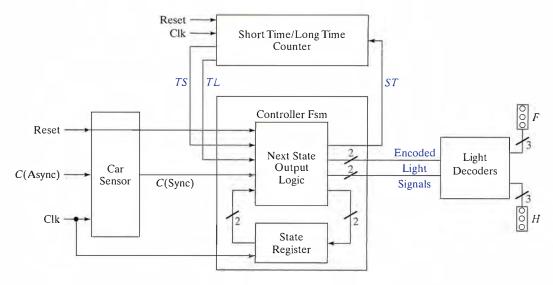

|            | 9.5 Case Study: Traffic-Light Controller 439                                                                                                                                                                                                                                                                                     |  |  |  |

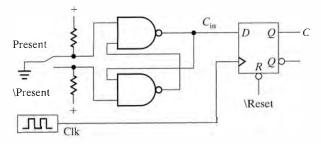

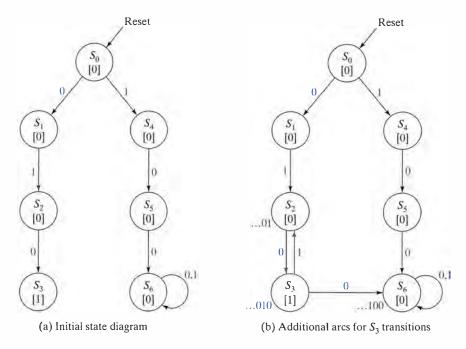

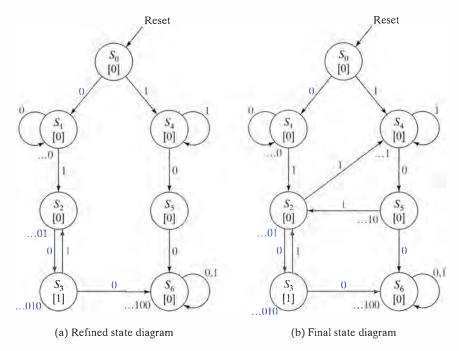

|            | 9.5.1 Problem Decomposition: Traffic-Light State<br>Machine 439                                                                                                                                                                                                                                                                  |  |  |  |

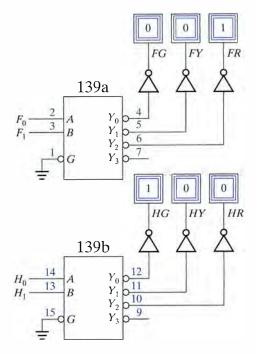

|            | 9.5.2 PLA/PAL/ROM-Based Implementation 442                                                                                                                                                                                                                                                                                       |  |  |  |

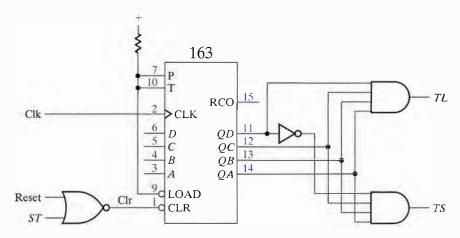

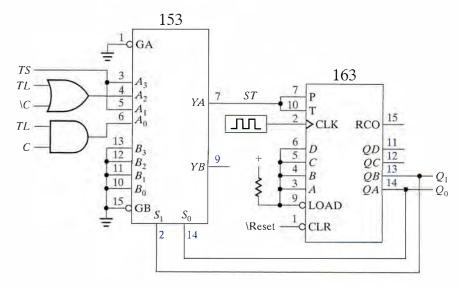

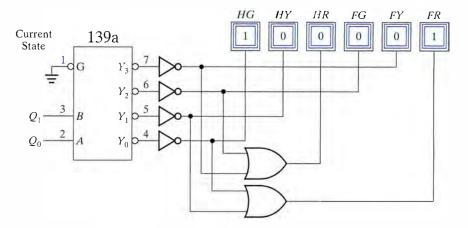

|            | 9.5.3 Counter-Based Implementation 443                                                                                                                                                                                                                                                                                           |  |  |  |

|            | 9.5.4 FPGA-Based Implementation 445                                                                                                                                                                                                                                                                                              |  |  |  |

|            | Chapter Review 446 Further Reading 447                                                                                                                                                                                                                                                                                           |  |  |  |

|            | Exercises 447                                                                                                                                                                                                                                                                                                                    |  |  |  |

|            | Exercises 447                                                                                                                                                                                                                                                                                                                    |  |  |  |

| Chapter 10 | Case Studies in Sequential<br>Logic Design 452                                                                                                                                                                                                                                                                                   |  |  |  |

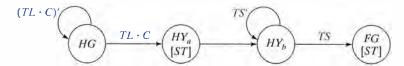

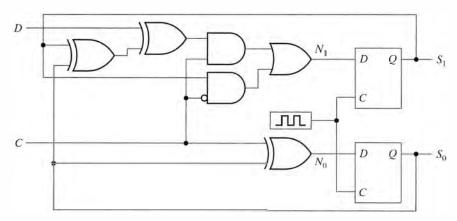

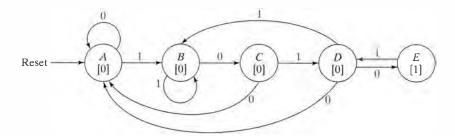

|            | 10.1 A Finite String Recognizer 452                                                                                                                                                                                                                                                                                              |  |  |  |

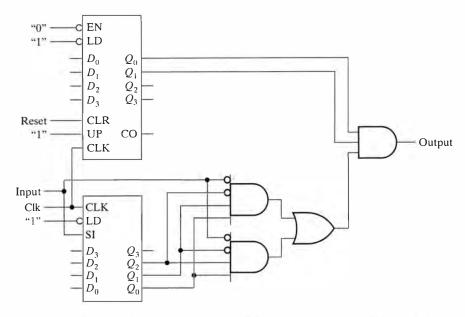

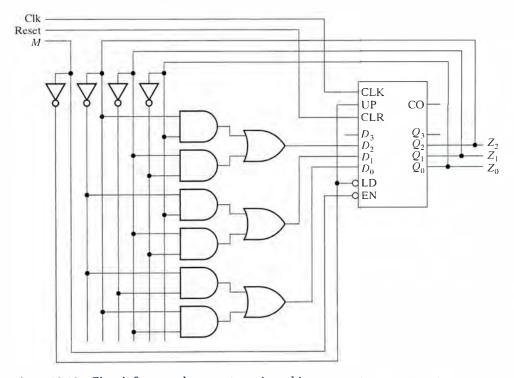

|            | 10.2 A Complex Counter 460                                                                                                                                                                                                                                                                                                       |  |  |  |

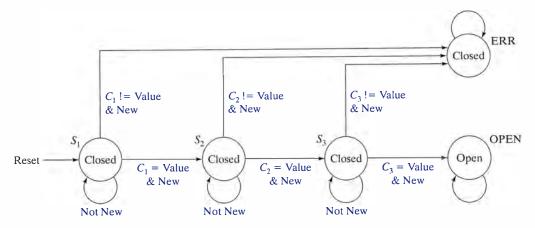

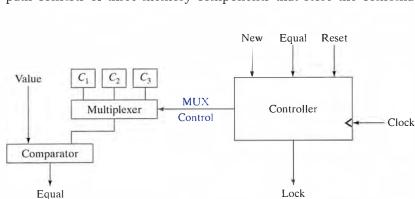

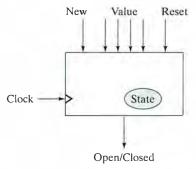

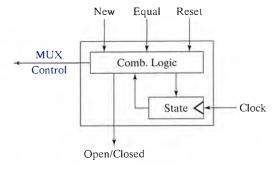

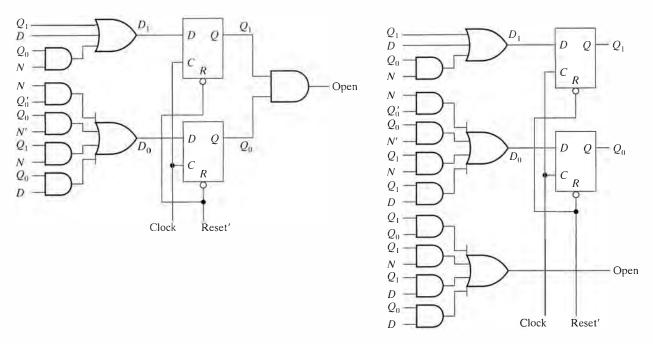

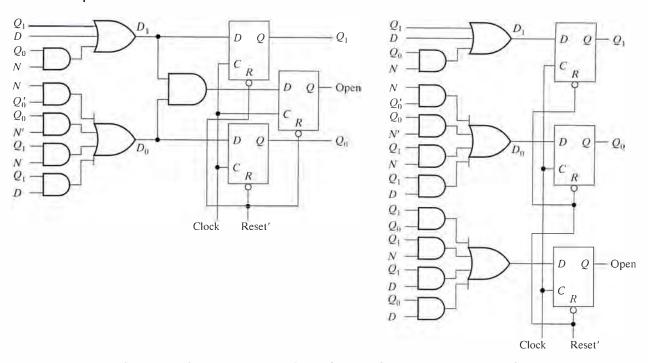

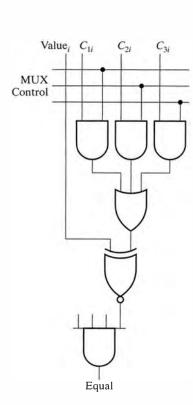

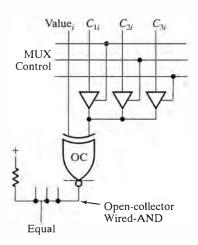

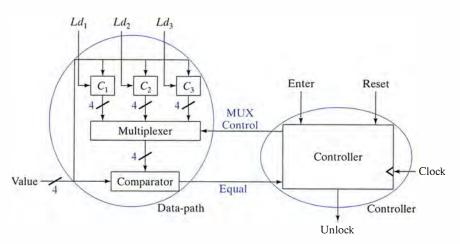

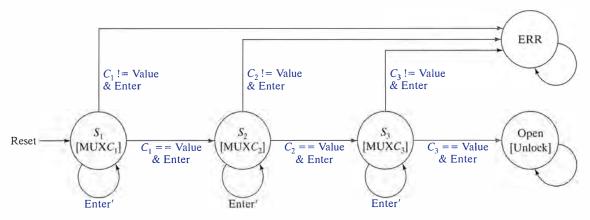

|            | 10.3 A Digital Combination Lock 463                                                                                                                                                                                                                                                                                              |  |  |  |

|            | 10.4 A Memory Controller 467                                                                                                                                                                                                                                                                                                     |  |  |  |

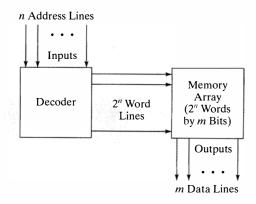

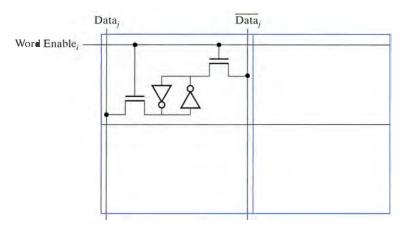

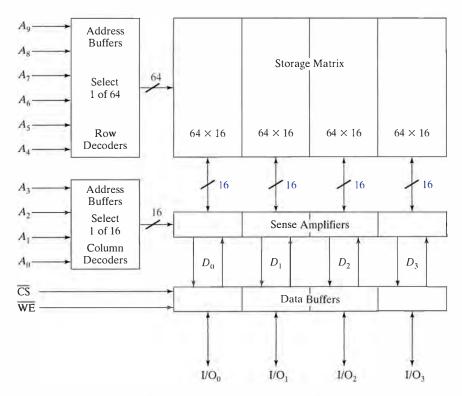

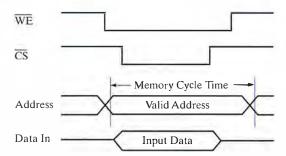

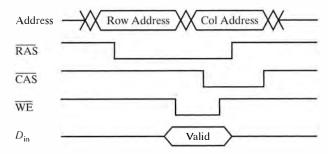

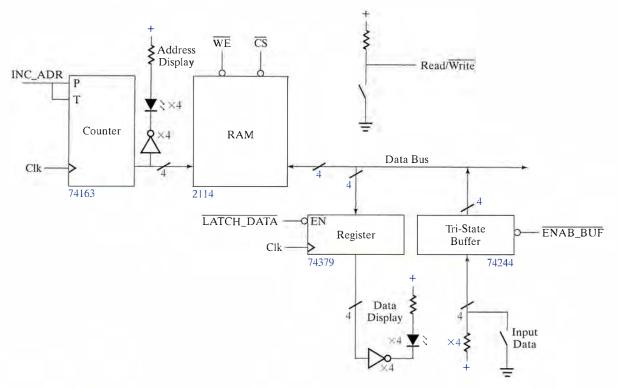

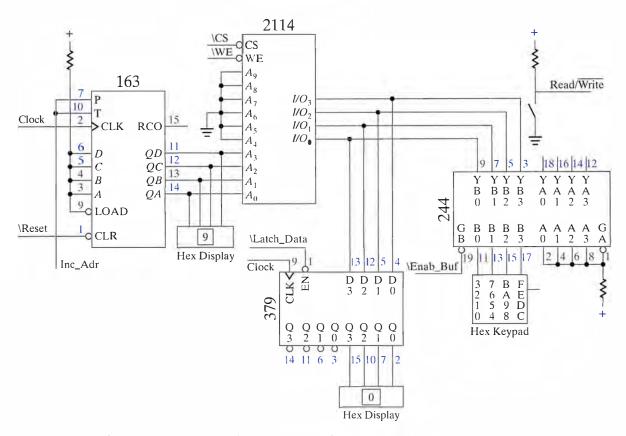

|            | 10.4.1 RAM Basics: A 1024×4-Bit Static RAM 467                                                                                                                                                                                                                                                                                   |  |  |  |

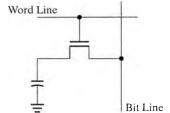

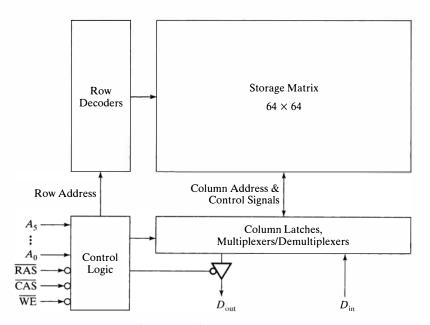

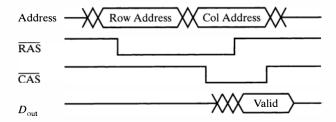

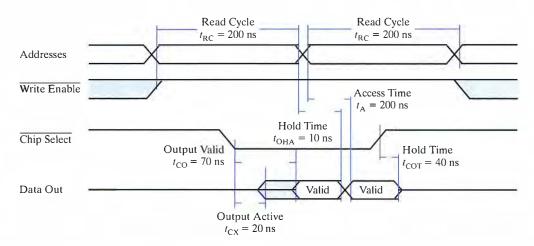

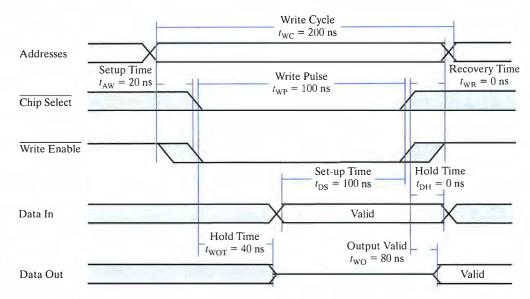

|            | 10.4.2 Dynamic RAM 470                                                                                                                                                                                                                                                                                                           |  |  |  |

|            | 10.4.3 DRAM Variations 474                                                                                                                                                                                                                                                                                                       |  |  |  |

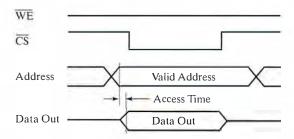

|            | 10.4.4 Detailed SRAM Timing 475                                                                                                                                                                                                                                                                                                  |  |  |  |

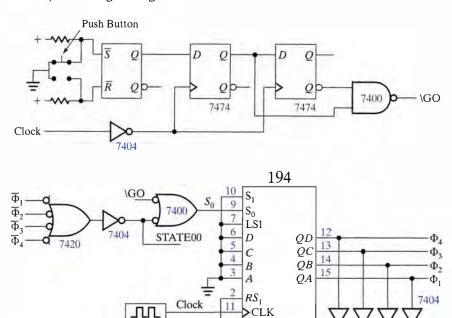

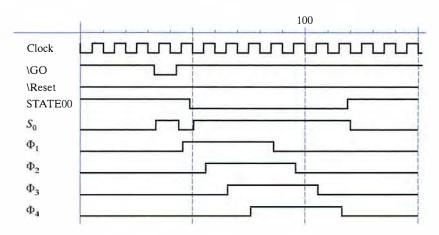

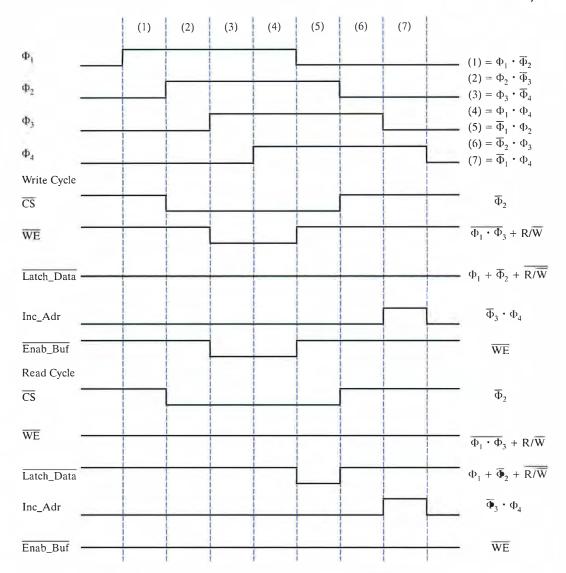

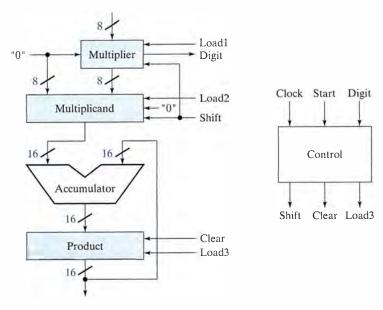

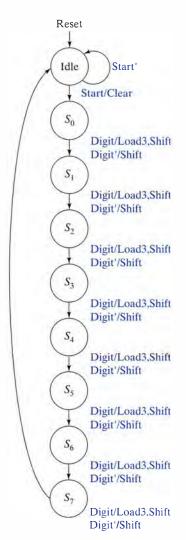

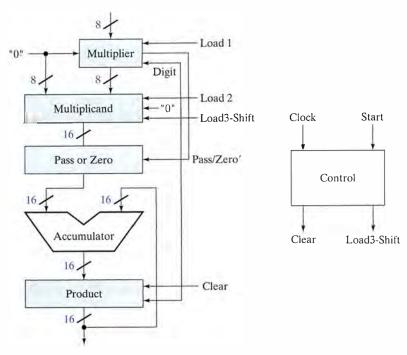

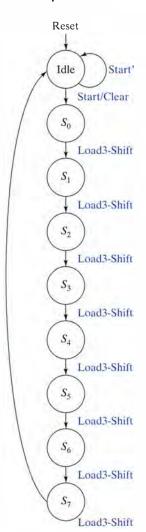

|            | <ul><li>10.4.5 Design of a Simple Memory Controller 477</li><li>10.5 A Sequential Multiplier 482</li></ul>                                                                                                                                                                                                                       |  |  |  |

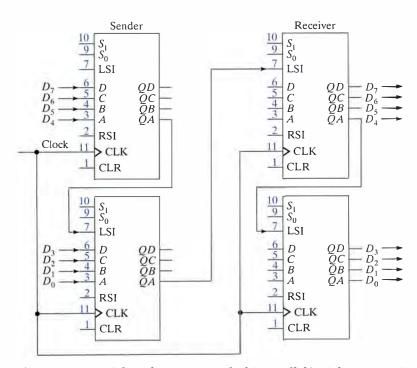

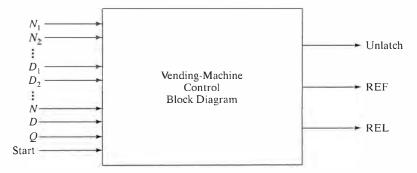

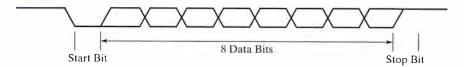

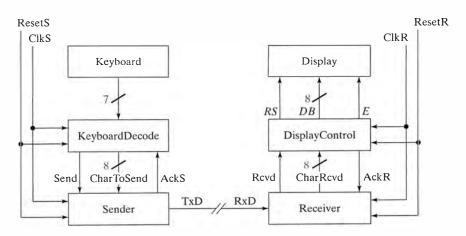

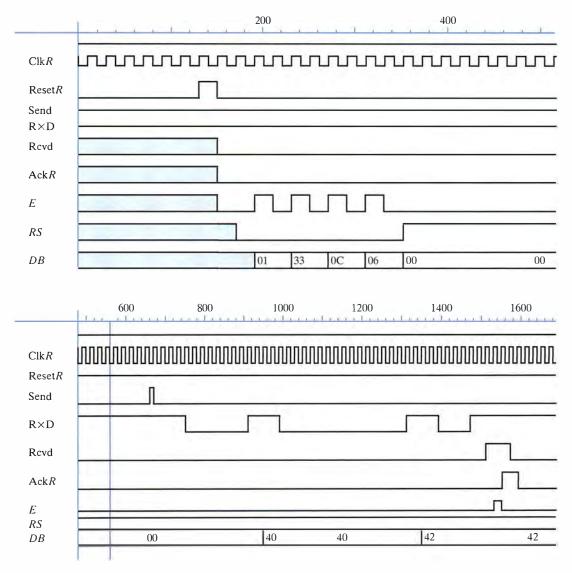

|            | 10.6 A Serial Line Transmitter/Receiver 487                                                                                                                                                                                                                                                                                      |  |  |  |

Chapter Review 499 Further Reading 499

Exercises 500

#### Epilogue 509

| Appendix A I | Number S | vstems | 511 |

|--------------|----------|--------|-----|

|--------------|----------|--------|-----|

| Δ1 | <b>Positional</b> | Number | Notation | 511 |

|----|-------------------|--------|----------|-----|

|    |                   |        |          |     |

- A.1.1 Decimal Numbers 511

- A.1.2 Binary, Octal, and Hexadecimal Numbers 512

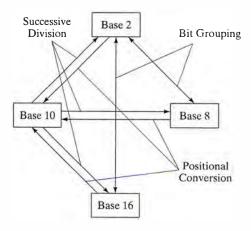

### A.2 Conversion Between Binary, Octal, and Hexadecimal Systems 513

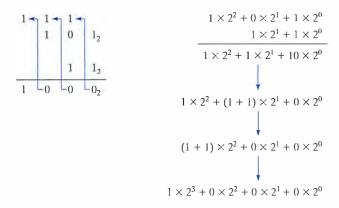

- A.2.1 Conversion from Binary to Octal or Hexadecimal 513

- A.2.2 Conversion from Octal to Hexadecimal and Vice Versa 514

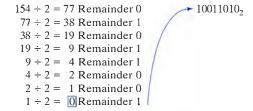

- A.2.3 Conversion from Base 10 to Base 2: Successive Division 514

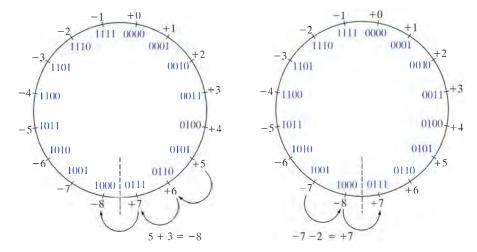

#### A.3 Binary Arithmetic Operations 516

- A.3.1 Addition in Positional Notation 516

- A.3.2 Subtraction in Positional Notation 518

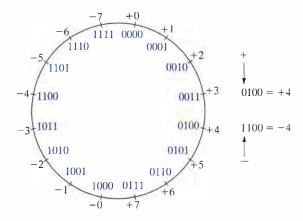

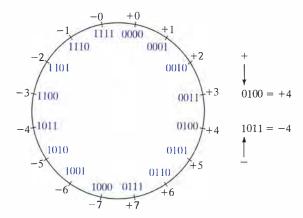

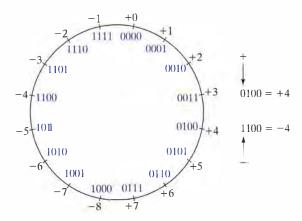

#### A.4 Representation of Negative Numbers 520

- A.4.1 Sign and Magnitude 520

- A.4.2 Ones-Complement Numbers 521

- A.4.3 Twos-Complement Numbers 522

- A.4.4 Addition and Subtraction of Numbers 524

- A.4.5 Overflow Conditions 526

#### A.5 BCD Number Representation 527

Appendix Review 528

Exercises 529

#### Appendix B Basic Electronics 533

#### **B.1 Basic Electricity** 533

- B.1.1 Terminology 533

- B.1.2 Fundamental Quantities and Laws 534

#### **B.2 Logic Gates from Resistors and Diodes** 536

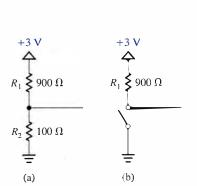

- B.2.1 Voltage Dividers 536

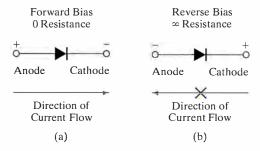

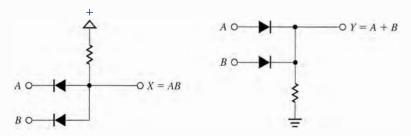

- B.2.2 Diode Logic 537

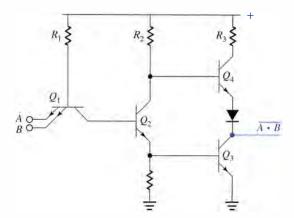

#### B.3 Bipolar-Transistor Logic 538

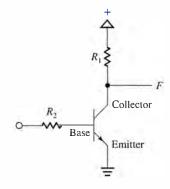

- B.3.1 Basic Bipolar-Transistor Logic 539

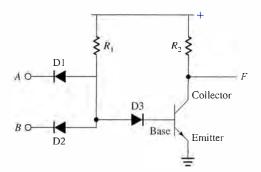

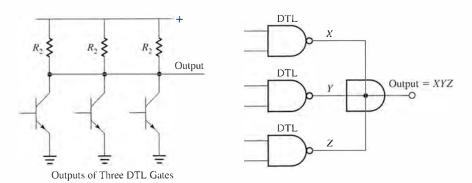

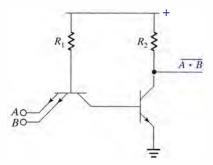

- B.3.2 Diode-Transistor Logic 539

- B.3.3 Transistor-Transistor Logic 541

- B.3.4 TTL Circuits and Noise Margin 542

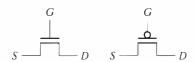

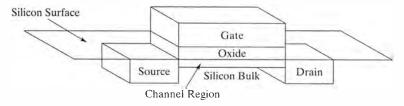

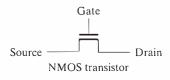

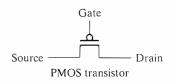

#### **B.4 MOS Transistors** 543

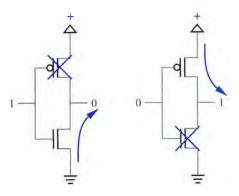

- B.4.1 Voltage-Controlled Switches 543

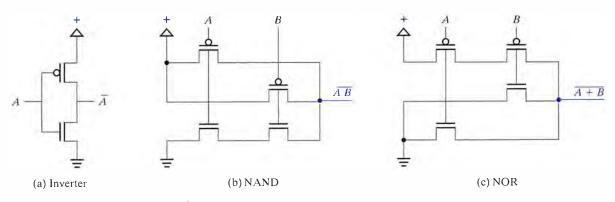

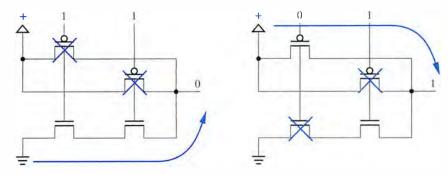

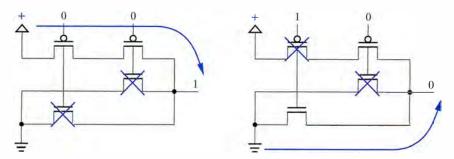

- B.4.2 Logic Gates from MOS Switches 544

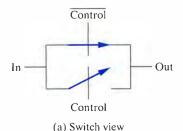

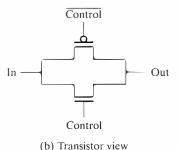

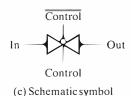

| B.4.3 CMOS Transmission Gate 546                                 |     |

|------------------------------------------------------------------|-----|

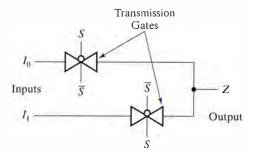

| B.4.4 Switch and Steering Logic 547                              |     |

| B.5 Elements of the Data Sheet 554                               |     |

| <b>B.5.1 Simple Performance Calculations</b>                     | 556 |

| B.6 Schematic Documentation Standards 55                         | 6   |

| B.7 Practical Aspects of Inputs, Outputs, and Clocks 560         |     |

| B.7.1 Switches and LEDs as Inputs and Outputs 561                |     |

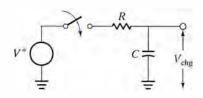

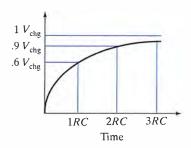

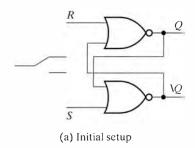

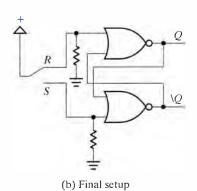

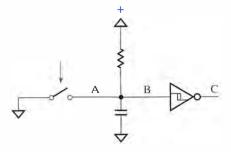

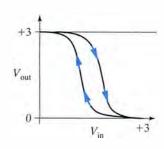

| B.7.2 Debouncing Switches 562                                    |     |

| Appendix Review 564                                              |     |

| Exercises 565                                                    |     |

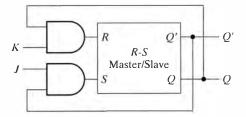

| Flip-Flop Types 566                                              |     |

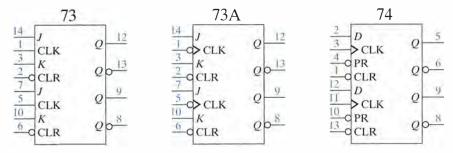

| C.1 Flip-Flop Components 566                                     |     |

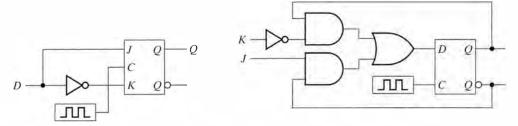

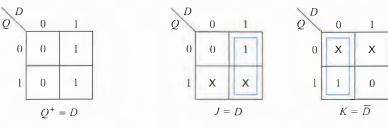

| C.2 Realizing Circuits with Different Kinds<br>of Flip-Flops 568 |     |

| C.2.1 Conversion of One Flip-Flop Type<br>to Another 568         |     |

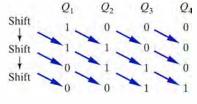

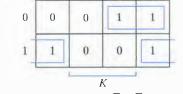

| C.3 Shift Registers and Counters 570                             |     |

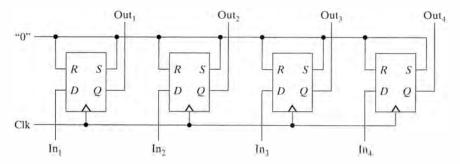

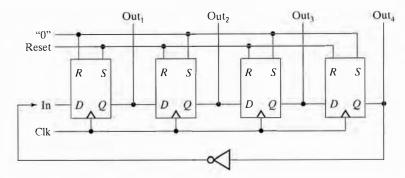

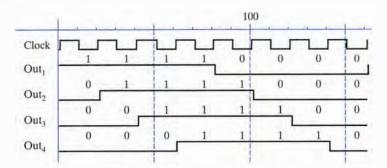

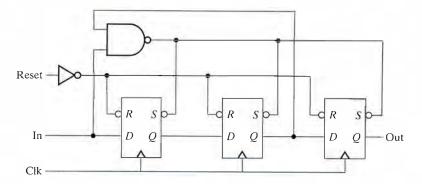

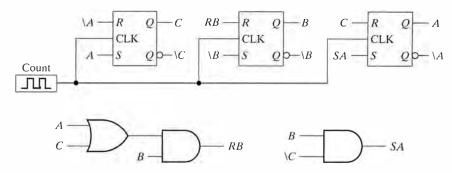

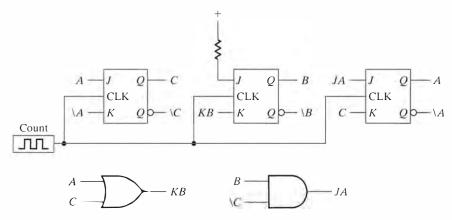

| C.3.1 Implementation with<br>R-S Flip-Flops 572                  |     |

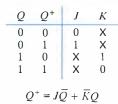

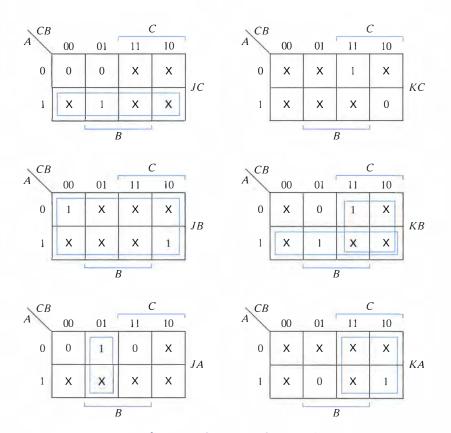

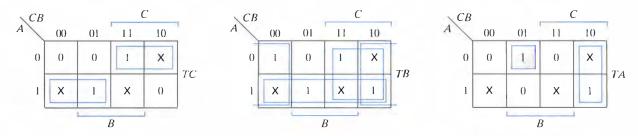

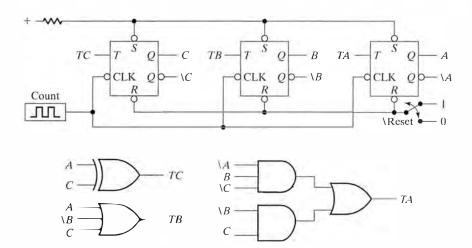

| C.3.2 Implementation with<br>J-K Flip-Flops 574                  |     |

| C.3.3 Implementation with <i>T</i> Flip-Flops                    | 576 |

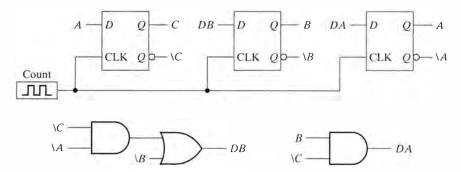

| C 3.4 Implementation with D Flin-Flons                           | 576 |

C.3.5 Comparison and Summary 578

Appendix Review 579

Exercises 579

Index 581

Appendix C

# **Preface**

#### A Second Edition

In the decade since the first edition of this book was published, the technologies of digital design have continued to evolve. The evolution has run along two closely related tracks: the underlying physical technology and the software tools that facilitate the application of the new devices. The trends identified in the first edition have continued stronger than ever and promise to continue for some time to come. Specifically, programmable logic has become virtually the norm for digital designers and the art of digital design now absolutely requires the software skills to deal with hardware description languages.

No longer do we see the familiar yellow cover of the TTL Data Book on every designer's bookshelf. In fact, for many application areas, even small programmable logic devices (PLDs), the mainstays of the 1970s and early 1980s, are rapidly disappearing. The burgeoning market for smaller, lower power, and more portable devices has driven high levels of integration into almost every product. This also has changed the nature of optimization; the focus is now on what goes into each chip rather than on the collection of individual gates needed to realize the design. The optimizations of today are more and more often made at the architecture level rather than in the switches.

Hardware designers now spend the majority of their time dealing with software. Specifically, the tools needed to efficiently map digital designs onto the emerging programmable devices that are growing ever more sophisticated. They capture their design specifications in software with description languages appropriate for describing the parallelism of hardware; they use software tools to simulate their designs and then to synthesize it into the implementation technology of choice. Design time is reduced radically as market pressures require products to be introduced quickly, at the right price and performance.

Although the evergrowing complexity of designs necessitates more powerful abstractions, the fundamentals haven't changed. In fact, the contemporary digital designer must have a broader understanding of the discipline of computation than ever before, including both hardware and software. In this second edition, we provide this broader perspective.

#### Changes from the First Edition

There are many changes from the first edition that can be grouped into four rough categories. First, we updated the hardware technologies

discussed in the book. Second, we added a more complete, if nevertheless introductory, treatment of the software tools that are now so commonplace in the designer's tool kit. Third, we responded to the comments and suggestions received over the years by the many faculty and practitioners who have used the book. Finally, we rationalized the organization of the text so that concepts, technologies, tools, and practical matters were more clearly defined.

#### New Introduction

The introduction has been changed from one that focused on the process of design to one that introduces the concepts of computation, encoding, and sequencing. This sets out a better road map to the rest of the book and provides a rationale for its organization. Rather than discussing the design process in the abstract, we now include many more case studies to help the student gain that understanding by seeing the process in action.

#### Repartitioning of Material

Each of the two major sections on combinational and sequential logic was divided into a set of chapters. These first cover the fundamental concepts, then describe the principles of manipulating the logic into different forms, followed by a discussion of the optimizations and tools that are available, and concludes with an overview of the technologies available to build logic circuits. Each is capped by a set of comprehensive design case studies that make each of the issues concrete.

#### More Emphasis on Programmable Logic

We have added new material on the latest programmable logic technologies that have quickly become the dominant style for realizing digital designs. We do not attempt to provide all the information needed to work with any one technology. Those used will vary dramatically from institution to institution. Therefore, the book needs to be supplemented with a laboratory guide that covers the specifics of a particular installation. In this text, we focused on the underlying concepts. We expect laboratory guides to be available in the form of web-based materials that can be easily customized to the variety already out there and updated as new technologies emerge.

#### Inclusion of Hardware Description Languages

HDLs are now given a more central role to reflect their total acceptance by the design community over the past 10 years. We describe only the basics of one of the dominant languages, namely Verilog, focusing on describing behavior, as well as covering the basics of HDL simulation models. We highlight the power of the languages in making designs more parameterizable and customizable and designers more efficient.

#### New Design Case Studies

Nothing helps students learn design as much as designing for themselves. The next best thing is to provide a large collection of examples where the intuitions and rules of thumb are discussed explicitly. The hope is that this will help bootstrap new digital designers into the world of practical applications rather than the drill problems that were the norm in simpler times. There are many new and extensive design examples sprinkled throughout the text and in two large case study chapters focusing on combinational and sequential logic.

### Elimination of Chapters on Datapath, Control, and Register-Transfer

We decided to remove the last two chapters of the first edition, that focused on datapath and register-transfer design, and a simple processor as an in-depth design case study of the interaction of control and datapath. While these topics are without a doubt important, on reflection we felt they are better left for a more extended study of digital design than could be included within the page limit of this edition. Instead, we chose more intensive coverage of programmable logic and HDLs, with extensive but smaller design examples spread throughout the text. We plan to make supplementary materials on the eliminated topics available on the web.

#### Navigating the Book

The book is organized into 10 chapters and three appendices. Chapter 1 is an overall introduction to the field. Chapters 2 through 5 cover combinational logic. Chapters 6 through 10 cover sequential logic. The three appendices provide some potentially useful background material that may have been part of other courses in a computer or electrical engineering curriculum.

Chapter 1 is an ambitious attempt to introduce many of the concepts of digital design through a short history of the evolution of digital hardware and two simple examples. Many may find that it introduces too many concepts too quickly for students to grasp their importance. However, this was not the intent. We fully expect students to be somewhat overwhelmed by the number of new concepts that come up in the discussion of the example. The purpose of the chapter is to provide an aerial view of the field so that students find it easier to see how the pieces they will see, in much greater detail and depth in later chapters, fit together coherently. It is certainly possible to replace this chapter with a more traditional introduction.

The next four chapters lay out the concepts of combinational logic design, closing with a set of comprehensive examples.

Chapter 2 covers the basics of combinational logic from simple gates to their time behavior. It lays out the concepts of two-level and multilevel logic and motivates why we would want to simplify logic. Some of the basic machinery for manipulating logic is presented with an emphasis on pencil-and-paper methods.

Chapter 3 delves into methods for working with combinational logic. It begins by describing the algorithms inside of today's CAD tools and ends with an overview of hardware description languages and uses Verilog to demonstrate key elements. Included is a discussion of the discrete simulation concepts that help to clarify the language constructs. There is probably not enough detail to make this book the sole resource for laboratory work with CAD tools. We wanted to keep the book focused on key concepts rather than on details of particular tools. It will need to be supplemented with appropriate manuals for the particular tools students will find in their own laboratories. This chapter also covers timing issues in more detail, including hazards and hazard-elimination strategies.

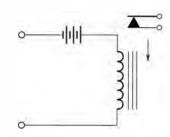

Chapter 4 presents the full range of implementation technologies available to the logic designer for combinational logic. It is paired with Chapter 9 that does the same for sequential logic. Chapter 4 starts with basic logic gates (as in the traditional TTL-based courses), but quickly progresses to programmable logic (PLDs and two-level forms) and then to field-programmable gate arrays. We also discuss other types of logic constructs such as tri-state and open-collector logic. Basic electronics to support this discussion are in Appendix B.

Chapter 5 culminates the combinational logic section of the book with seven examples of increasing complexity. We emphasize problem solving from the initial specification and have provided considerable discussion of how to transform an initial informal description of the problem into precise logical statements while keeping track of the assumptions that are being made. Our goal in this chapter is to show the range of logic design and how to judge design tradeoffs and take advantage of optimization opportunities.

The remaining five chapters do the same for sequential logic what the Chapters 2 through 5 did for combinational logic.

Chapter 6 begins this section by introducing the idea of circuits with feedback and how they can be analyzed. We develop the basic elements of sequential logic, latches, and flip-flops by recapitulating their evolution. This is coupled with a discussion of the timing methodologies that make it practical to build large sequential logic systems. These methodologies are illustrated with simple sequential systems of shift registers. The chapter concludes with a continuation of the exposition of hardware description languages started in Chapter 3 and extends it to basic sequential logic elements.

Chapter 7 covers the central concept of finite state machines. It begins by using counters as a simple form of FSM and then moves on to the basic Moore and Mealy models for organizing sequential behavior. Like Chapter 2, it concludes by motivating the various optimization opportunities.

Chapter 8 extends the basic ideas of Chapter 7 and expands on the details of FSM optimization by treating state minimization, state encoding, and FSM partitioning, in turn. Each of these is illustrated with examples that highlight the tradeoffs at each stage of optimization. An

additional section at the end of the chapter provides some guidelines for structuring FSM descriptions in HDLs.

Chapter 9 concludes the discussion of implementation technologies. It recapitulates all the technologies used for combinational logic introduced in Chapter 4 but focusing on their sequential logic elements.

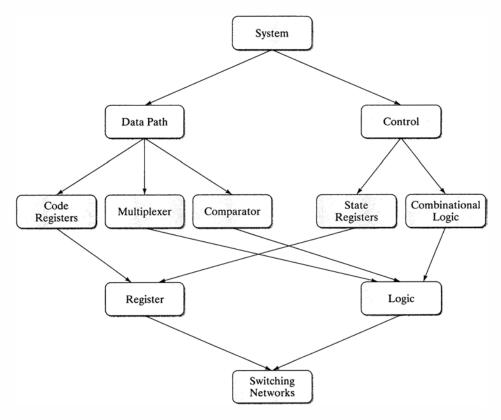

Chapter 10 is a large chapter with six comprehensive design examples that bring to practice all the concepts in the text. It begins with the sequential logic example from Chapter 1, now discussed in full detail, to tie back to the start of the text and ends with the serial transmission of characters from a keypad to display. The latter examples focus on the partitioning of design problems into communicating pieces along two dimensions: parallel state machines and partitioning into datapath and control.

The three appendices cover number systems, basic electronics, and flip-flop types. The first two cover concepts that students are likely to have already seen in mathematics, physics, electrical engineering, or computer science introductory courses. They are not intended to be extensive treatment of these topics but only provide the background most directly connected to the main topics of this text. The appendix on flip-flop types is provided for historical completeness.

#### The Complete Teaching Package

The material in this book easily fills a quarter-long course and can be comfortably covered in a semester-long course. In fact, it is likely that supplemental topics, governed by the place in the curriculum the semester-long course occupies, can and should be included. These could be: more in-depth discussion of CAD algorithms including their data structures, efficiency, and implementation; further discussion of design tradeoffs in a particular implementation technology such as FPGAs; a larger design problem that can serve as a term project to highlight issues of scale and debugging; and topics from computer organization emphasizing partitioning into data-path and control and optimizations of both. Of course, individual instructors may also find that re-ordering some of the material makes more sense in their environments. For example, it is certainly possible to proceed by following the two sections in parallel rather than serially. Chapter 2 plus 6 and 7 can be paired, followed by 3 and 8, then 4 and 9, with the larger design examples of 5 and 10 together at the end. Many topics can also be skipped altogether. For example, CAD tools and their algorithms may be relegated to another course. Similarly, HDLs do not need to be included if the design environment focuses on schematic-level design. In the technology dimension, FPGAs can be skipped as they may be included in a later course on more advanced design methods. Our goal in organizing the book was to make it easier to make these customizations.

Finally, we are making a wealth of supplementary material available to course instructors and students. Our publisher's web site includes:

- A set of CAD tools that supports all the concepts presented in this text;

- A comprehensive set of lecture slides;

- Samples of possible laboratory assignments and projects;

- Solutions to all the problems in the text; and

- Supplementary material on computer organization for those that include that material in their introductory logic design classes.

We hope you will agree with us that this second edition is a worthy successor to the first.

RANDY H. KATZ GAETANO BORRIELLO

## Introduction

#### Introduction

Computer hardware, in its short 50-year history, has experienced the most dramatic improvement in capabilities and costs ever experienced by humankind. Computing devices are now ubiquitous in our daily lives. They've come a long way since they were machines used exclusively by a few scientists. They are used now by an ever-growing portion of the world's population. From their birth as automatic machines for arithmetic calculations, computers now are part of everyday appliances such as microwave ovens, anti-lock brakes, media players, and pocket calendars. We no longer think about computers explicitly when we use the devices that they make possible. CD and DVD players let us listen to music and watch movies—but they are, in fact, computing devices in that they include several microprocessors as well as other digital hardware (see Figure 1.1). Just think how the telephone has become a highly integrated communication system with many components. A cellular phone allows you to make and answer calls from just about anywhere in the world. As electronics shrink in size, we also benefit from lower power requirements and smaller batteries that last longer. A music player has become portable, holds thousands of songs, and can play them for hours without recharging. Your home phone or cable line now also lets your computers access an unprecedented wealth of information and services over global networks.

Logic design is one of the disciplines that has enabled the digital revolution which has dramatically altered our economies, communication systems, and, consequently, our lives. Not only have the hardware components evolved dramatically, but the tools of the logic designers' trade are also quite different that what they were even a short 10 years ago.

Any introduction to this subject must necessarily begin by defining what we mean by design and logic design, in particular. We will then provide some historical perspective by quickly reviewing the evolution of the underlying technology that makes our digital world possible. We'll conclude the chapter with some examples of logic design that will serve as a preview to the remainder of the text.

Figure 1.1 The internal electronics of a digital video disk (DVD) player consist of several computing devices that process the light levels from a reflected laser beam and transform them into an audio stream for speakers or headphones and video stream for a display.

#### 1.1 Dissecting the Title

#### 1.1.1 Design

Design is the process of coming up with a solution to a problem. To do this, we not only have to understand precisely what the problem is, but also the constraints our solution must meet. We can't come up with solutions that require an unlimited amount of money or carelessly waste resources and pollute our environment. Constraints can arise from physical limitations or even from aesthetic and subjective criteria. For example, if we are designing a building, the problem may be to create 50,000 square feet of space that will make office workers very productive. Physical constraints on the building design could include limits on its height, how far it can go underground, the number of offices with windows, the number and type of common spaces such as conference rooms, kitchens, and atria, and all the service utilities the building will need. The building's external design also will have to fit in to the surrounding neighborhood and be welcomed by its neighbors. These are, of course, only a small part of the constraints that architects must manage when designing a solution. The architect must also ensure that the building is completed within its cost budget, that it can be heated and cooled efficiently, and that noise levels generated by ventilation systems are within tolerable limits for the people that will occupy the building.

We recognize building design as a very complex process. To handle this complexity, we've developed an important strategy based on the tried and true divide-and-conquer approach. We do this so that we can divide our problem into smaller sub-problems. Human beings are only able to keep so many details and their interrelationships in their

heads at one time. By dividing the building into its constituent parts, and using a team of designers (or in this case, contractors and their subcontractors) each working on their own parts of the whole, we are better able to manage a large design task. Each component is now a design problem for its respective designer who may in turn choose to divide it down further. In our building example, these will include office layouts, window frames, ventilation systems, etc. Note that the decomposition of the design tasks is often functional and not spatial. For example, the elevator design may be further decomposed into the design of the shafts, mechanical and electronic controls, as well as their relationship to fire safety rules. The building's chief architect is responsible for bringing these pieces together to form the complete building. Although, the architect may have some influence over the design of these pieces, it is likely that, due to cost considerations, the choice may be limited to predesigned solutions available only in specific pre-fabricated configurations. Good communication between all the contractors involved in the construction of the building is essential in guaranteeing that inconsistencies and errors are caught as early as possible when there is more time to make adjustments. It is difficult to widen an elevator shaft, for example, after the building's skeleton is already completed.

Most of the objects we design are themselves going to consist of components. In fact, the design process turns out to be very similar in a wide range of disciplines. This may not be obvious at first. Clearly, a civil engineer designing a new highway interchange has a different set of problems than a computer engineer building a new holographic display. But it turns out they are much more similar than they first appear. Each has to breakdown the problem into smaller pieces, each has to deal with constraints beyond their control, each has to put all the pieces together to solve the bigger problem, each has to be part of a larger team and/or manage a part of the effort, etc.

For example, designing a new software application is not really all that different from our building example. When we pick a particular computing platform (a processor and its memory system) it imposes limitations on our software. Some programs may need more memory resources or not run fast enough on the platform we chose. User interface concerns also have an influence on our software's design. Our software designer will be trying to be efficient and will want to reuse utilities available from the computer's operating system or parts of software packages that were previously written and with which she is already familiar. Thus, the software will have to be structured in such a way to take advantage of the pieces that may already be available. Finally, the software required may be too large for one individual, group, or even company, and pieces will have to be sub-contracted to others to complete. Our designers will have to make sure they communicate regularly and clearly so that they don't make any mistakes that will cost them time later when they try to pull all the pieces together.

Complex systems, such as our building or personal computer software, require us to adopt a design methodology if we are going to be able to manage the process efficiently and effectively. A design methodology is a domain-specific formalization of the design process into a set of well understood steps. Architects have developed a design methodology that involves contractors and builders, materials suppliers, community and municipal agencies, and the eventual occupants of the building. An automobile designer also has a methodology but it is likely to be quite different from that of the building architect and include much more concern with safety, reusing parts from existing car models, and streamlining the assembly line.

Design has three important facets. It is a creative process of coming up with a vision of the solution. It is an engineering process of evaluating tradeoffs and making decisions among many alternatives. It is an optimization process of choosing the best combination of components to realize the vision. In this text we'll be working on all three facets.

#### 1.1.2 Logic Design

The components that the digital designer has at the ready are made from digital electronics. Combinations of switches, built from semiconductor transistors, form the basis of all of today's digital hardware. We generally refer to an interconnected collection of switches as a circuit. Individual switches are not the only building blocks available. There are also higher-level circuit modules such as logic gates and memories that use switches already pre-arranged in an efficient and flexible way. The logic designer's job is to choose the right components to solve a logic design problem. Constraints in logic design are often related to some combination of size, cost, performance, and power consumption. Cost and size are very closely related. A component's complexity is determined not only from all the switches it contains but more importantly from all the wires used to connect the switches together. A component's size usually has a direct relationship to the cost of manufacturing the component. Performance and power consumption are determined by the particular arrangement of switches and wires, the underlying materials from which they are constructed, their size, and how fast they are switched on and off. Interestingly, as integrated circuit technology further shrinks the size of transistors and the width of wires, it is the wires that are coming to dominate designers' concerns as they already add more to the size of the circuit and to its performance concerns than do the transistors.

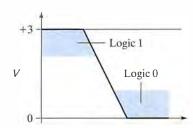

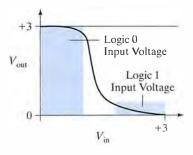

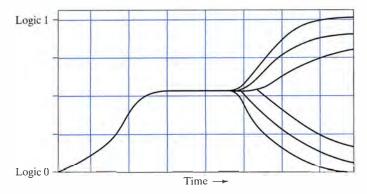

All digital components have a set of input wires and a set of output wires both of which carry digital logic values. In other words, wires that are set to some voltages we have agreed to will represent two different values, that is, 0 and 1. Of course, in the real world, we have continuous phenomena and the wire can in fact be set to any voltage. In the case of digital electronic circuits, any voltage below some level, say 1 volt, is interpreted as a logical 0 any voltage above some other level, say 2 volts, is viewed as a logical 1.

Arbitrary information can be represented using this digital abstraction. Binary notation is used to represent integers as well as floatingpoint or even complex numbers through the use of a collection of wires each of which is a binary digit and together form the number. More interestingly, the color values for each pixel of a digital image or the volume of the sound created by a speaker can also be represented digitally. The digital abstraction is extremely powerful because it is more tolerant to variations in voltages which are difficult to make precisely identical in every single copy of a circuit. Furthermore, 0s and 1s can be used to represent analog values to arbitrary precision and have led to a powerful convergence of information that lets us store, transfer, and display information ranging from telephone calls to digitized maps to movies to e-mail messages using the same basic concept, namely, binary voltage levels on wires.

The transistors inside a digital component react to the voltage levels on the input wires. Changes in voltages cause transistors to change their conductivity, that is, switch their state, and thereby cause a change in some of the voltage levels on the output wires of the component. We often refer to the inputs causing a value to be applied to the outputs. For example, we may have a circuit with two inputs and one output where the output is set to one if both inputs are also one. This is referred to as an AND logic gate because both the first input and the second input must be at voltage levels corresponding to a 1. We'll later see a wide range of logic gates. These types of circuits, where inputs directly influence the value on outputs, are referred to as combinational logic circuits. They form the basis of all our computational elements including components that can add, subtract, or even multiply.

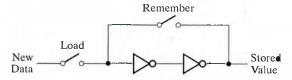

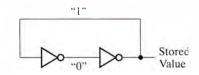

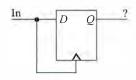

Other types of digital circuits are referred to as sequential logic circuits. Their outputs not only react to the current values on the input wires but also to the past history of values on those same input wires. Thus, sequential circuits have memory in that they will remember the past inputs and react to the current inputs while taking their history into account. A simple example of a sequential logic circuit is a memory component that has two inputs and one output; the output is set to the same value as one of the input wires when the second input wire signals it to do so. The input value *sampled* in this manner is then held indefinitely until the circuit is signaled again to store a new value. These types of circuits form the basis of memory devices that allow our computers to store and recall data as well as keep track of the step in a sequence of instructions, embodied in a computer program, they are to execute next.

Logic design is a set of abstractions and methodologies that let us devise, understand, and manipulate large collections of digital circuits. We've seen one abstraction already, namely, using 0 and 1 to represent all sorts of data. We'll see several others in this chapter and many others in the remainder of the text. Design methodologies are important procedures for ensuring a principled and effective design process. We'll be developing several of these for different types of digital logic. Finally, we'll also develop ways of transforming and optimizing our circuits so that they can have a better chance of meeting design constraints and be efficiently implemented using the particular components we may have at our disposal.

Figure 1.2 Photographs of a late 19th century phonograph and a late 20th century portable digital video disc (DVD) player (not to scale).

#### 1.1.3 Contemporary Logic Design

Logic design has been around for at least 150 years. In that time, there has been continuous evolution of the abstractions, the basic building blocks, and design methodologies, the rules for putting the building blocks together. We can extend our analogy to building design as it also has evolved, using different materials, and different methods, for example, new materials as well as new earthquake and fire safety codes. In digital design, the changes have been quite dramatic and there are several important trends that are still at work.

First, our systems are becoming ever more complex as we integrate more functions into a device and perform computations on ever larger quantities of data. Just compare the complexity of a turn-of-the-19th-century phonograph and today's DVD players (see Figure 1.2). The older device is mostly mechanical and dealt with continuous values in both time and amplitude (loudness of the sound), namely, the vibration of a needle on a vinyl record and the amplification of that vibration into a vibration of the speakers. The DVD player reads digital data representing the sounds using a laser that doesn't even touch the spinning plastic disk. The information read from the disk can be in any form including audio, video, and text. These binary numbers are translated into either vibrations of a speaker through a digital-toanalog converter that translates a number into a proportional voltage level, or into images by turning pixels on and off on a screen. Furthermore, enough of these numbers have to be read and translated every second to make the sound seem continuous to the human ear rather than choppy. The phonograph consisted of a handful of moving parts. A DVD player includes several microprocessors operating on a digital representation of images and sound giving us access to any part of a film instantaneously with no degradation over time.

Second, the design of today's digital systems is happening in a much faster time frame as the demands of the consumer market place inexorable pressure on products to have a wide range of features appropriate for different uses and situations. New models of phonographs were introduced every few years. In contrast, there are dozens or, perhaps, even hundreds of new models of DVD players produced each year. Each model solves the problem of getting images and audio from the DVD disc to the screen a bit differently and thus provides for choices in cost, form-factor, user interfaces, and advanced features.

Third, and finally, the cost of digital hardware has become so low and its performance so high that we no longer need to be concerned with engineering the absolutely lowest cost solution. It is becoming more important to design rapidly and getting it right the first time. Getting new products out to market quickly is what generates the largest profits.

These three trends have led to a radical change in the methodologies of logic design over the past 10 to 15 years. First among these is automatic generation of logic circuits using software tools. We can now specify the functions we want our circuits to perform using a highlevel specification language and have a logic compiler refine and transform that specification into a set of components. Second, we have created digital components that do not have fixed functionality but can be used to perform a wide range of functions based on a configuration performed after they are manufactured. This provides immense economies of scale, as we no longer need to carry large inventories of different digital components. Third, the emphasis has now shifted from the crafting of the implementation (i.e., the arrangement of switches into circuits) to the crafting of the specification. Designers focus more on getting the high-level specification right, to meet all the functional requirements of their product, rather than on arrangements of transistors. They rely on the compilation tools to determine the best set of components to use and how they will be configured.

Contemporary logic design now faces many of the same problems as software design. Designers want to work using specification languages at ever higher-levels of abstraction. They can be much more productive at higher levels, as there are fewer components to consider. However, they also want to ensure that the resulting design will meet the design constraints. Hardware designers are interested in ensuring that an appropriate collection of components is used that costs no more than necessary and will perform their computations quickly enough. Similarly, software designers are also concerned with performance and the memory requirements of their applications. Both types of designers also need to be able to visualize their specifications and debug them when their artefacts do not behave as intended. In logic design, simulation tools, that mimic the behavior of the real physical components but allow the designer to easily peek inside, are an essential part of the designer's arsenal serving similar functions as the debugger does for software designers. Another important similarity between hardware and software exists in their respective methodologies for design. Both hardware and software designers understand the need to re-use as many portions of designs as possible. It is still an engineering art to devise components that can be used in many different contexts. This is crucial to making the design process more economically efficient.

#### 1.2 A Brief History of Logic Design

We will begin the history of logic design in 1854 when George Boole invented an algebraic system for manipulating logical propositions. Boolean algebra is now the mathematical foundation of logic design. It forms the basis for the optimization of digital logic much in the same way we use arithmetic algebra to transform expressions on variables into equivalent ones that have fewer operations. For example, by using the distributive law to perform one less multiplication in an algebraic expression (a \* x + b \* x = [a + b] \* x).

Claude Shannon's seminal paper in 1938 established a link between Boolean algebra and the switches used in the relay circuits of the day. This was an important step in moving Boolean algebra from the realm of abstract mathematical logic to physical devices that actually computed a logical expression with voltages.

The first general-purpose digital electronic computer, the electronic numerical integrator and computer (ENIAC), was designed and build by J. Presper Eckert and John W. Mauchly at the University of Pennsylvania between 1943 and 1946. It was the first machine to have all the classical elements we now consider part of a modern computer. This was a big advance from relays because vacuum tubes were much smaller and could switch much more quickly than relays. These machines could perform several hundred multiplications per minute with 18,000 vacuum tubes—a huge advance from the hand-operated calculating machines, which were then the mainstay of scientific computation at the time. However, it did weigh 30 tons, consumed 200 KW of power, and occupied 1500 square feet. Even with these staggering dimensions, its principal disadvantage was that vacuum tubes were highly unreliable and over the course of a day an average of 50 tubes had to be replaced.

The invention of the transistor in 1947 heralded the dawn of the integrated circuit age. Highly reliable semiconductor switches replaced vacuum tubes very quickly. The first commercially available transistor computer was the Ferranti Mark I in 1951. Soon thereafter, scientists were able to manufacture multiple transistors simultaneously using the technique of photolithography, invented in 1957, to create patterns of semiconductor materials using light-sensitive materials and chemical etchants. This was a revolutionary change as circuit elements no longer needed to be wired together individually but could be manufactured as an already wired-up circuit. Thus began the era of integrated circuits, which led to the first microprocessor: the 4-bit Intel 4004, in 1971, was first used in the Busicom electronic calculator.

By the end of the 1960s, logic designers had available a large catalog of logic components (such as those described in the then ubiquitous Texas Instruments TTL data book, the preeminent catalog of available parts). Arbitrary logic circuits could be built from these basic primitives which were mass produced in great quantities and

so beginning the inexorable advance toward cheaper electronic circuits with higher reliability that continues to this day.

Programmable logic arrays, collections of switches in regular arrangements that could be configured by the logic designer to implement any one of a huge quantity of possible functions, soon arose to increase levels of integration and to make it easier for designers to change the wiring pattern between logic functions. These devices started to see wide use with the introduction of Monolithic Memories' Programmable Array Logic (PAL) line of components in 1975.

With the increased levels of integration in digital circuits and the need for designers to program their reconfigurable logic components came the development of logic synthesis tools. Starting from Boolean algebra expressions, these software packages could determine the precise configuration of logic arrays to implement the specified function and therefore free designers from the drudgery of dealing with every single switch and allowing them to focus on higher level design. One can think of these early tools as the assemblers of their day, translating from assembly language to machine code. Their successors today are much closer to compilers for high-level languages (e.g., C, Java) and the software development environments that go with them (e.g., Visual Studio).

Today, we see the continued development of programmable logic, in the form of field-programmable gate arrays (introduced by Xilinx in 1984), which can now be reconfigured over and over again. This makes possible logic circuits that can be altered over time, field upgraded after a product has been purchased, or even re-programmed quickly enough from one use of the product to the next. Synthesis tools have followed closely with the appropriate compilation technology to configure these new types of components. Finally, the level of integration has continued to increase. We can now consider using many transistors just to give our circuits more flexibility rather than stingily allocating each individual transistor as in the early days of integrated circuits.

#### 1.3 Computation

Up to now, for most of you, computation has been an abstract process. You may have specified the steps of a calculation for a computer to execute but the details of how that computation is actually accomplished have probably been somewhat of a mystery. You may know that digital computers operate on binary digits (also called bits), 0s and 1s, and you may know how they represent integers and characters using strings of bits, usually 32- and 8-bits long, respectively. But what role do these strings of bits play in the execution of complex programs?

This text is about de-mystifying computation. It will guide you through the first steps in understanding how computers work. In the coming chapters, we'll see how to implement all the common

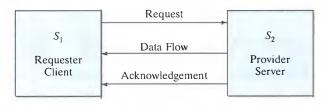

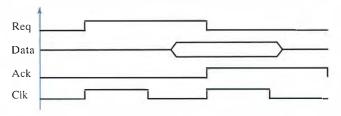

programming constructs, including variable assignment, arithmetic operations, conditional and iterative statements, and subprocedures. We will learn how to construct circuits that perform all these functions using a few simple primitive elements. In addition, we'll also see that circuits can perform functions in parallel, not just sequentially, and operate on arbitrary data types, not just bits and integers. After all, we can have many circuits working in parallel on different inputs. At a small scale, arithmetic circuits provide an excellent motivation for parallelism since we can work on the different parts of the strings of bits in parallel. At a larger scale we'll see how simple computers, working independently, can go about communicating and coordinating their activities.

#### 1.3.1 Switches, Relays, and Circuits

Switches are the basic building blocks of digital computers. The proper arrangement is the physical embodiment of abstract computations in digital circuits.

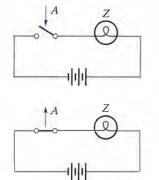

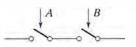

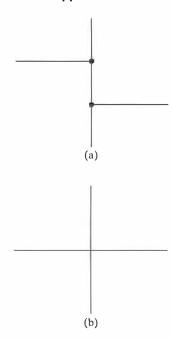

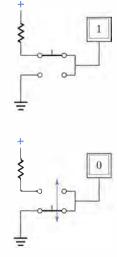

Let's review how switches work. In Figure 1.3, we show a simple switching network that is found in every home, probably in every room. A switch is used to disconnect a light bulb from its power source. If the switch is open, current does not flow through the circuit and the light bulb is off. If the switch is closed, then the light bulb is turned on as the battery's current can now travel through the light bulb and return to the battery—a completed circuit.

If we represent the state of the switch by using a Boolean variable, say A, that we set to 0 if the switch is open and 1 if it is closed, and represent the state of the light bulb using another Boolean variable, say Z, that we set to 0 if the bulb is off and 1 if it is on, then we can write:

$$Z = A$$

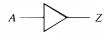

as a Boolean expression that represents the functionality of this circuit. If A is 0, then Z is 0 (switch open, light off) and if A is 1, then Z is 1 (switch closed, light on). We can also use the symbol in Figure 1.4 to indicate this circuit in a schematic drawing. Note the arrow shape indicating that the output Z is affected by the input A.

We can make our simple circuit a bit more interesting if we now add a second switch in series with our original switch represented by *A* (see Figure 1.5). We will represent this new switch with the Boolean variable *B*. Now the functionality of our circuit is such that both switches have to be closed for the bulb to turn on. We can write this expression as:

#### Z = A and B

to indicate that both *A* and *B* have to be 1. A circuit like this is commonly found in automobiles where the key activates one switch and the windshield wiper wand activates another. Both have to be *on*, that

Figure 1.3 A simple switching circuit found in every home shown with its switch in open and closed positions, respectively.

Figure 1.4 Schematic symbol for the simple circuit of Figure 1.3.

Figure 1.5 Two switches in series will close a circuit if both *A* and *B* are closed.

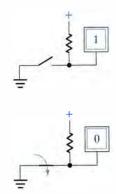

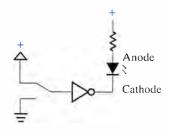

is, both switches have to be closed for the windshield wipers to work. The schematic symbol for AND is shown in Figure 1.6. Note that it also "points" in the direction of the output.

At this point, it is clear that we are thinking of 1 as having a meaning of *true* and 0 as *false*. This is, in fact, the common convention, and it makes sense in everyday English. However, the choice is really arbitrary. We'll see later on that it really doesn't matter what value represents true or false, just as long as we are consistent.

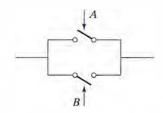

But let's continue on to another parallel arrangement for the two switches (see Figure 1.7). In this case, either A or B being closed will turn on the bulb. The current can flow through either path or both around the circuit. Our expression for this circuit is

$$Z = A \text{ or } B$$

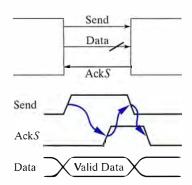

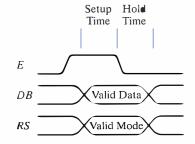

to indicate that either *A* or *B* or both have to be 1 for the bulb to be turned on. An example of this is also found in cars where the dome light will turn on whether the driver's or the passenger's door is opened. The schematic symbol for OR is shown in Figure 1.8.